- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

myRIO FPGA problem

12-23-2015 03:49 AM - edited 12-23-2015 03:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone.

I have some doubts about myRIO and its components and how they work but an specific doubt is this one:

I thought CPU on myRIO works with FPGA and its previous configuration so as the FPGA is configurated you can acces on RT Processor to the controls and indicators to manipulate them on the RT VI so when the FPGA is no configurated with its default personality it's suppoused to do not let me use myRIO APIs BUT I actually can use myRIO APIs.

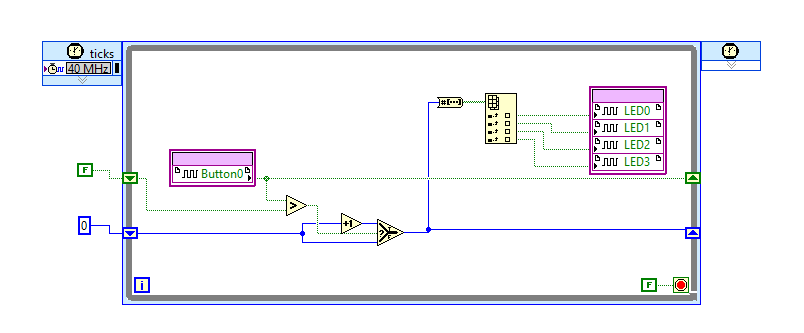

I download this VI on FPGA:

When I run this VI it look like all is working as the FPGA was its default personality.

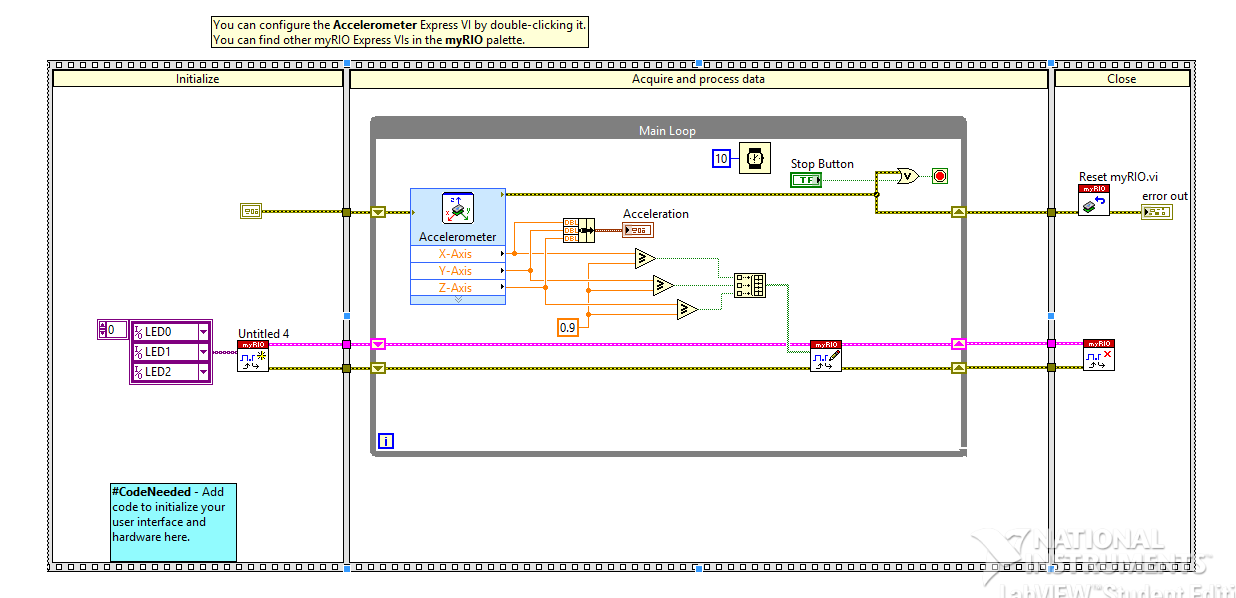

In an example of myRIO projects I found this in one of the VIs at the Chasis:

This VI contains the default FPGA personality in addition to code that generates a sine waveform and filtered sine waveform based on parameters set by RT Main.vi. Keeping the default personality allows you to continue using the myRIO APIs even after adding custom FPGA code.

So as I said, working with APIs in my RT VI should not be possible if my FPGA VI doesn't hace the default personality.

I would appreciate your answers and explanations.

Thank you.

12-23-2015 05:43 AM - edited 12-23-2015 05:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you use the myRIO API, it automatically loads and runs the currently selected personality to the FPGA, stopping any existing FPGA code that is running on the FPGA. There is some information about the default personalities and switching between them here: http://zone.ni.com/reference/en-XX/help/373925B-01/myriohelp/myrio_fpga_personalities/

If you want to write custom FPGA code, you can either:

1) Make a copy of one of the default personalities and customise it to add your in your own custom functionality. You can then select this customised personality and you will be able to use the myRIO API as well as the FPGA running your own custom code. Of course, if you remove any of the functionality from the default FPGA code, that functionality won't work with the myRIO API.

2) Write your own FPGA VI from scratch and call it using the 'open FPGA reference' method on the RT side. You cannot use the myRIO API if you do this.

For reference, there is a 'myRIO Custom FPGA Project' that ships with LabVIEW. The documentation for the template is here.