- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Subsequent delayed analog voltage generation with USB-X 6343 or 6353

09-05-2016 03:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

I need a delayed voltage signal or TTL after one immediately. To do so, I modified "Voltage - Finite Output" example vi following Dennis_Knutson advise in the 7th message here. You can see the modified vi in the attachment. Is it correct? Can I get deterministic time delay values lower than 1 ms with this way? (I know the hardware - USB-X 6343/6353 - is not a RTE or FPGA, but I have to try since no hardware I have except these guys, trying my chance). Instead of voltage generation, can I do the same thing with counters? Regarding critical timings (lower than 1 ms), with which one should I try my chance?

09-06-2016 07:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi newbieeng,

I just want to check a few things. Are you wondering if it's possible to do this with the hardware mentioned, or if your code will accomplish this task? Is the code not working as expected?

Andrew B.

Applications Engineer

Application Engineer

National Instruments.

http://www.ni.com/support

09-07-2016 12:57 AM - edited 09-07-2016 12:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Andrew,

I was wondering if it is possible to do this task with this device and also with the code. I gave the code a try on the device. It popped up an error saying the number of samples must be the same for all channels. So I modified the program (attached). I thought I will be able to create delays lower than 1 ms by this way. Am I right?

And I am also stuck in the code about defined number of samples and sample rate to the basic function generator. I need only one high step signal not a pulse train. When I increase the delay time over 1 second, the code does not work. I think its about number of samples and sample rate and also frequency. How can I modify to code to solve this problem. Maybe, I could not have explained what the problem was, if I have a chance during the work hour, I will take a screen shot of waveform graphs during operation and attached to explain the problem clearly.

09-07-2016 03:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

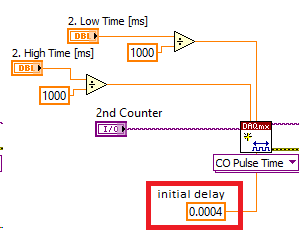

Can I also do the same task with counters? I modified finite counter output example vi and attached. Does it work for the same task?

09-07-2016 01:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As far as if the device is capable. The best place to look for that would be in the device manual. Some of the functionality in the VI isn't possible since analog triggering isn't capable on the 6343. This is the manual: http://www.ni.com/pdf/manuals/374567d.pdf

As far as the code goes, I'm still attempting to get it working on my end. Looking at your code, it looks like you have combined two examples together. Have you tried getting the examples to work separately before combining them?

Application Engineer

National Instruments.

http://www.ni.com/support

09-08-2016 02:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually, I did not combine codes. These two codes do the same task, however, one of them use AOs, the other one use counters. Yesterday, I check the code with counters with an oscilloscope. The code popped up an error about retriggerable function. It is not supported the error message says. Then I change delete that property node and decided to use "initial delay" on CO function. It works pretty nice for ms level, however, I observed some unintentional delays sometimes when I entered delay values lower than 1 ms like 0.4 ms. Anyway, I am still trying. I wish I could get reasonable results.

09-08-2016 12:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The minimum possible value for the initial delay is based on the clock. The attached code snippet will tell you what initial delay should be possible. If you exceed the minimum, then the value will coerce to it's minimum capable value. Could you check and see if the output of the property node is 1 ms.

Andrew

Application Engineer

National Instruments.

http://www.ni.com/support

09-09-2016 01:12 AM - edited 09-09-2016 01:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

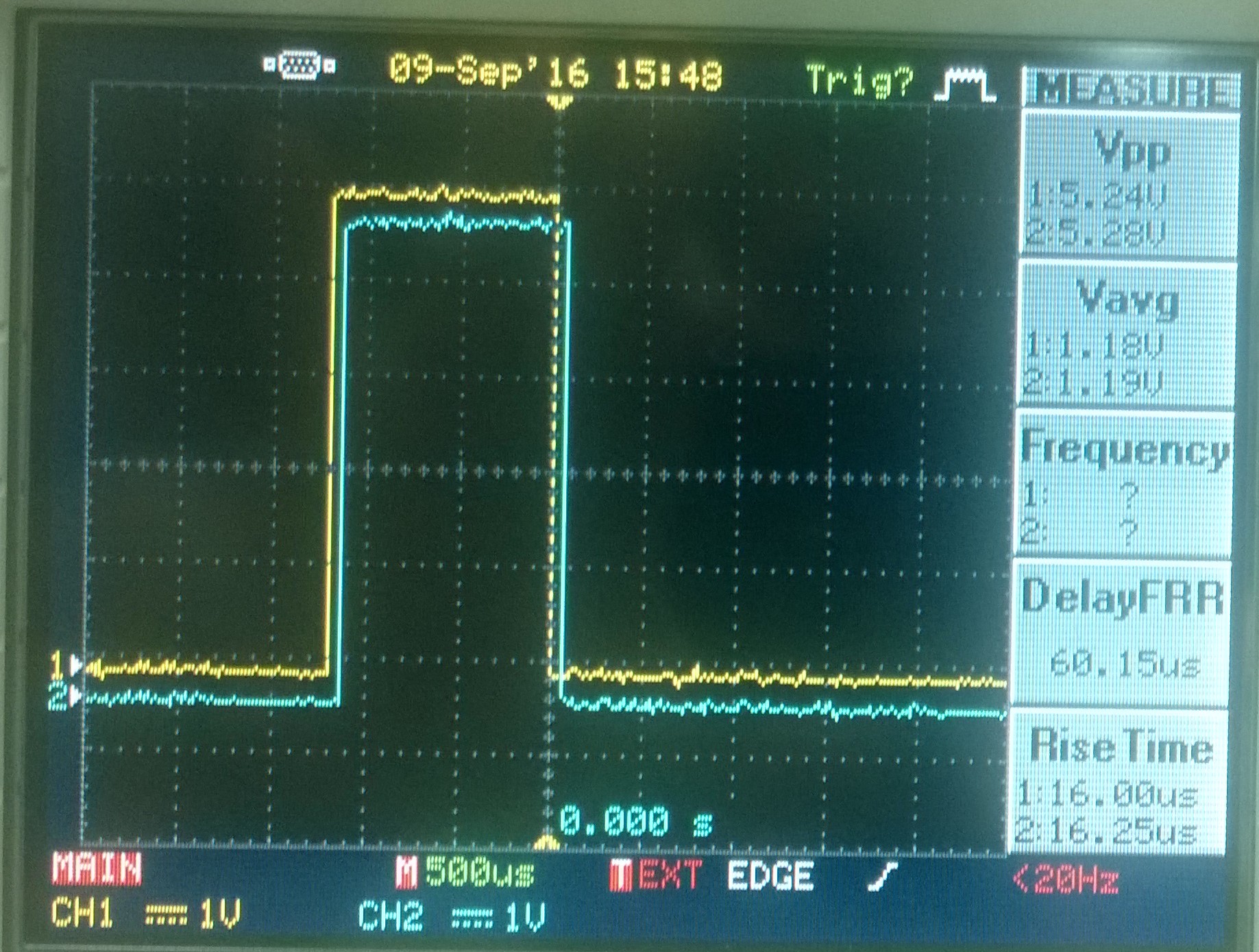

I tested the code with an oscilloscospe. I measured the delay between the first rising edges. The code worked perfectly. It can wait lower than 1 ms period. I can delay the second signal 0.2 ms. I think it is ok. I do not define the clock source by use of timing VI. I do not check which clock the device use as a default one. Should I define an implicit timing with clock source?

I will also check the delay with your code. I will let you know the result.

09-09-2016 08:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi again,

I tested your suggestion. It gives the exact value written, however, there is a little deviation from the desired value in real when I looked at the oscilloscope. You can see the results below.

09-21-2016 01:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry for the late response, but this is likely a hardware limitation. Depending on what rate you're sampling at, there is a greater potential error. What rate are you sampling at?

Application Engineer

National Instruments.

http://www.ni.com/support