- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VHDL code integration?

Solved!02-18-2015 02:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone,

We've been developing OFDM and SOQPSK-TG transmitter and receiver hardware in FPGA using the design suite. Previously we were using LabVIEW FPGA.

My question is, how do you import pre-written VHDL code to be compiled in the design suite? I cannot seem to figure out how to do this, which was possible with LabVIEW FPGA software. Which type of FPGA-targeted VI would you start with?

Thanks!

-Brian

Solved! Go to Solution.

02-18-2015 04:13 PM - edited 02-18-2015 04:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would definitely recommend trying to repair/reinstall VeriStand since you have the code working flawlessly on another set up (could be a corrupt install).

I not familiar with any cRIO hard drive test off the top of my head, but let me look into that and see if we can come up with anything.

Also, for best practices in VeriStand, the closest thing I can recommend is the Getting Started materials but this is probably not helpful to you. The next thing would be the actual training but I understand that may not be doable as well. Just from your description of your architecture, I do not see anything inherently wrong but I would have to take a look at the project itself to know for sure.

02-18-2015 04:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm having a hard time comprehending that response. In fact I think you may have posted to the wrong topic...I don't even know what VeriStand is.

02-18-2015 04:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am so sorry! I replied to the wrong forum! Completely my fault!

02-18-2015 04:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Wow for a second there I thought I was crazy! No worries ![]() . Hopefully another engineer will get back to me on this one.

. Hopefully another engineer will get back to me on this one.

02-19-2015 11:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Has no one else experienced this question?

02-19-2015 04:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So I was able to check with a few colleagues and confirm that LabVIEW Communications does not currently support VHDL integration as does LabVIEW FPGA.

02-19-2015 04:55 PM - edited 02-19-2015 05:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually, while it's not well supported, it's also not impossible...

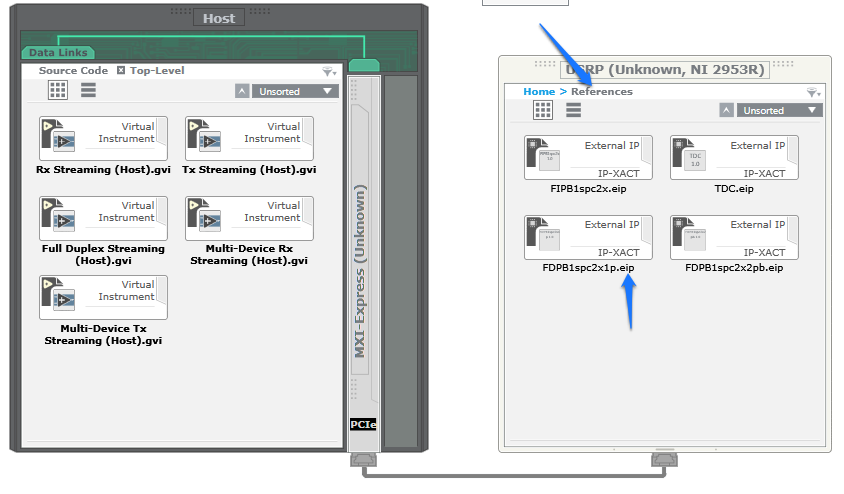

The general process is to create an IP-XACT file, and use that. There should be an example of what this looks like in the 579x or USRP sample projects.

TJ G

02-19-2015 05:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In LabVIEW Comms we use the .eip extension to pull external VHDL in using IP-XACT as a backing description of that IP. You can find them to your project under resources on the FPGA target.

The .eip file is an IP-XACT file and you should be able to follow the pattern of those files in one contained in the USRP sampleprojects to get your VHDL working.

04-08-2015 10:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

All,

We have a created a KnowledgeBase article which describes integrating 3rd party FPGA IP in LabVIEW Communication 1.0 in more depth.