Hello,

I'm trying to perform some operation in FPGA SCTL(200MHz) by reading a large block memory [Size : 16384]. There is a combinational logic before calling Read Memory node and after read memory.

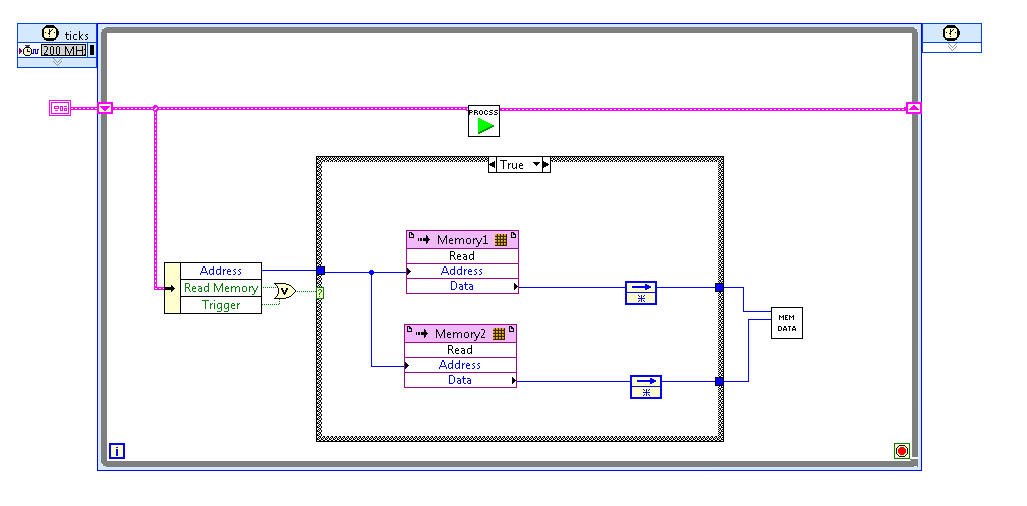

Code block is shown below,

The same code compiles without timing error if the memory size is small (1024 size for both the memory).

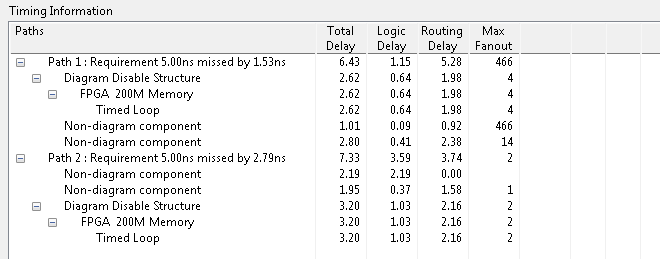

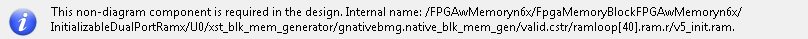

If the memory size is set to 16384 (both memory1, memory2 ), compilation fails with the below non-diagram error message in the timing violation window.

Non - diagram error 1 :

Non - diagram error 2 :

Please help us to find a best way to handle this.

Target Details : 7962 FlexRIO card is used

LabVIEW version : LabVIEW 2012

Memory type is set to Block Memory. I use "Never arbitrate" option.