- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA (PXI-7852R) Phase Locked Square Wave DIO

05-26-2014 11:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Attached is a screen shot of a piece of code that creates square waves. Sadly, if the channels are set to different frequencies they are not phase coherent. Looking at all three square wave outputs with an oscilliscope and triggering on one of the channels I see that the other two channels are not "stationary", but rather moving relative to the channel with which I am triggering.

How do I rememdy this issue? I would like the other channels to not move relative to the channel with which I am triggering no matter what frequency I set them to.

My thoughts are that I need to program a trigger into the FPGA code. Any thoughts?

Thanks in advance!

05-27-2014 10:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi dthrash,

Are these frequencies exact multiples of each other? Double check the Frequency (period/tick) calculation inside the Express VIs and make sure they are integer multiples. The drift from this offset would be consistent though, so that may not completely fix things. Additionally, you should try placing each step of the parallel sections of code in a sequence structure; currently it looks like those steps might be getting out of sync at each iteration and introducing a bit of a phase difference.

05-27-2014 01:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your response Matt_L

I double checked frequencies and they are integer multiple of one another. I also added the sequence structure (pictured below). Sadly there was no improvement.

Any other ideas?

05-27-2014 02:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What are your frequencies? Is it possible to generate them exactly from the 80 MHz clock?

Lynn

05-27-2014 05:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, exact submultiples would be fine for now. Just as long as they are phase matched

05-28-2014 03:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I should have clarified earlier, but with the sequence structure can you try placing each element in a different frame? So all of the cluster reads in one frame, the waveform generation steps in one frame (I think this step would have the greatest effect), and the outputs in the last frame.

05-28-2014 04:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Matt

attached is my attempt to follow your instructions. Did I get it right this time?

Sadly with frequencies of 1 kHz and 20 kHz the relative phase was still not constant.

05-28-2014 08:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

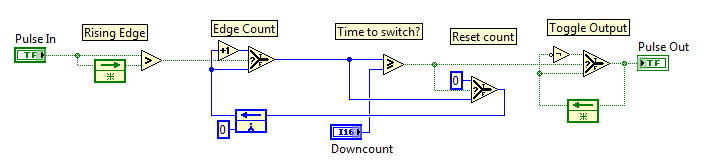

I would suggest using the frequency generator for the highest frequency signal, then downcount to get the other two signals. For example, the 1 kHz signal would change on every 10th rising edge of the 20 kHz signal. This would guarantee that both signals rise at the same time. You could base the third signal off either of the other two signals. You would want to trigger off the slowest signal to get phase matching on the faster signals.

Bruce

Ammons Engineering

05-29-2014 08:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Bruce,

Thanks for your suggestion. I dont have a lot of experience with programing pulse counters with LabVIEW FPGA. Can you point me towards any examples to get me started?

Thanks!

05-29-2014 09:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here is a block diagram that does what I suggested:

I have attached this VI in LV 2013 format.

Bruce

Ammons Engineering