- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Modify digital pulse width inside loop

Solved!06-14-2016 07:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I'm looking for a solution that allow to modify digital pulse width inside while loop.

Thanks in advance

Solved! Go to Solution.

06-14-2016 08:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here is working code, but there is drawback - pulse width cannot be larger than "Pulse advancement" time.

Ceratinly the solution will come from triggering ?

06-14-2016 09:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here I tried to implement triggering: analog value generated on rising edge from digital output with delay, specified by "Pulse advancement" parameter.

Doesn't work: analog output isn't generated at all, the width of digital pulses doesn't correspond to specified value (the width is too narrow)

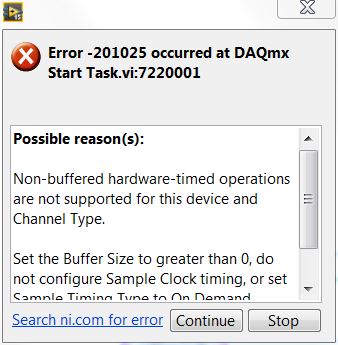

Finally once I stop VI, the following error appears:

Any ideas ?

Thanks

06-14-2016 10:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For narrow digital pulses the workaround is including of the "Wait until done" block.

Concerning analog output triggering still have no solution

06-14-2016 10:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Will it work if you set pulses to run continuously? (add Daqmx timing in Implicit mode, continuous). You can modify high and low times on the fly without stopping task.

Then, on pulse width value change event you modify your task

I did not understand how do you want your pulse to interact with analog output - do you want change to happen "pulse advancement" after digital pulse?

WIll "hardware timed single point" mode of the analog generation work? Clock - counter output.

Is your pulse width important? You can set low time to determine period of pulses, and high time to determine analog output delay (set clock to happen on falling edge).

What board is it? What are your times and resolution? I doubt it is possible to set additional delay without one more counter for fast processes.

For slow processes you can set buffered triggered acquisition (2 points). Timing is pulse advancement value. Start-stop task in a loop. Also commit task before loop - it will greatly speed up start-stop.

06-15-2016 04:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Alexander_Sobolev a écrit :Will it work if you set pulses to run continuously? (add Daqmx timing in Implicit mode, continuous). You can modify high and low times on the fly without stopping task.

Then, on pulse width value change event you modify your task

I did not understand how do you want your pulse to interact with analog output - do you want change to happen "pulse advancement" after digital pulse?

WIll "hardware timed single point" mode of the analog generation work? Clock - counter output.

Is your pulse width important? You can set low time to determine period of pulses, and high time to determine analog output delay (set clock to happen on falling edge).

What board is it? What are your times and resolution? I doubt it is possible to set additional delay without one more counter for fast processes.

For slow processes you can set buffered triggered acquisition (2 points). Timing is pulse advancement value. Start-stop task in a loop. Also commit task before loop - it will greatly speed up start-stop.

Thanks Alexander,

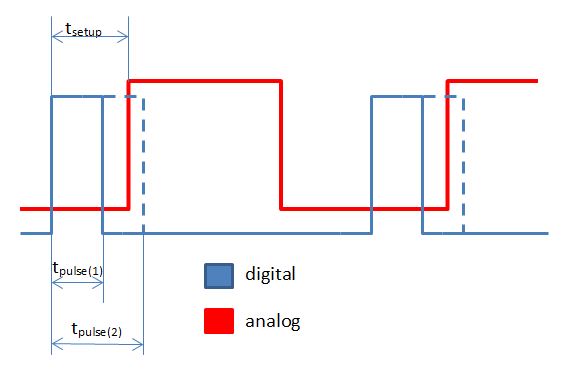

Here is the sketch of waht I want to implement:

Here are keypoints:

- digital pulse is armed before analog signal change its state

- the digital pulse width must be adjustable ... for the moment the precision isn't concerned ... just adjustable (e.g. tpulse(1) and tpulse(2) on the picture)

- the setup time (i.e. time between digital pulse is armed and analog signal change value) also must be adjustable ... here the accuracy is concerned

- the board is USB-6251 (also USB-6343)

Will it work if you set pulses to run continuously?

You mean specify "Continuous samples" on analog output DAQ timing ?

You can modify high and low times on the fly without stopping task. Then, on pulse width value change event you modify your task.

If here you mean the digital output, it was already done (and it works) in my previous verison of VI

You can set low time to determine period of pulses, and high time to determine analog output delay (set clock to happen on falling edge).

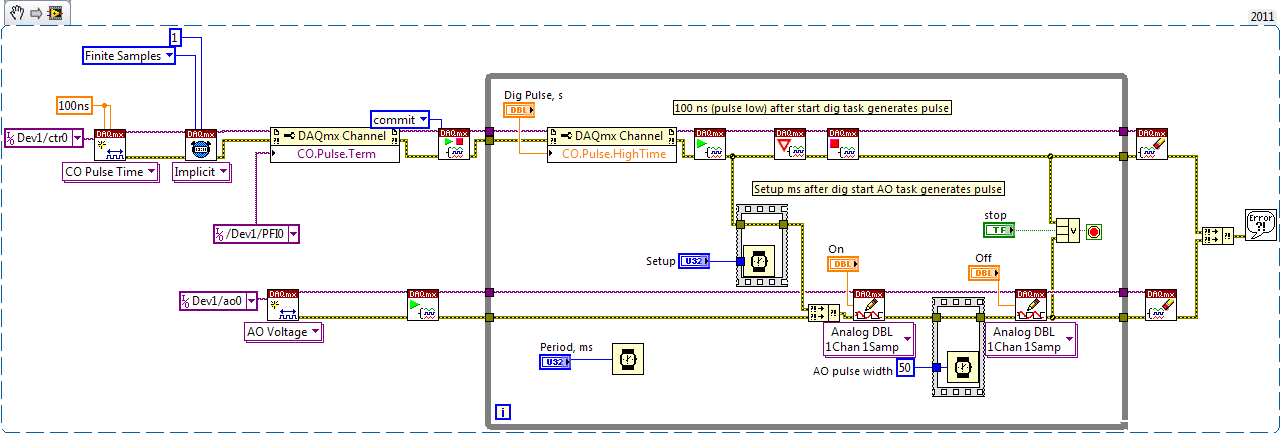

Here is what I tried (if I properly understood your suggestion)

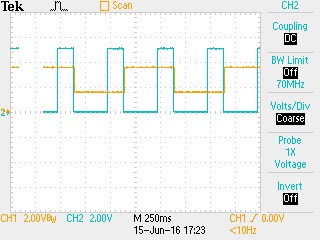

Setup [ms] parameter has no impact (if more than 0) on digital signal: analog signal chnages the value once digital goes to LOW state (please see the oscilloscope snapshot below)

In other words I can't realize VI behavior that corresponds to the tpulse(2) case (as shown on the image at the TOP of this post)

I think the only way to synchronize update of analog value with rising edge of digital pulse is using trigger ... but all examples I examined until now don't correspond to my case.

06-15-2016 09:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Check the dataflow and counter output operation with single pulse

FIrst counter generates low time, then high time.

Then your AO task needs to set voltage to ON after Dig pulse. After AO pulse width it needs to set it to low

If software jitters are small enough for you, you could have used USB-6008 (250$), not Xseries 1600$ - it seems an overkill. X series can do this job with sub microsecond resolution.

06-15-2016 09:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can you try attached VI? It is only configuration of tasks, without modification of parameters on the fly.

Ctr0 is running continuously, with required period and pulse width

Ctr1 is intermediate counter. Normally it would generate a pulse where your analog pulse should happen ("setup" after ctr0 pulse rising edge). But Event behaviour property changes it to pulse on edges instead of toggling state.

Analog output task is continuously regenerating values from a buffer, so it is alternating between on and off. Clock is ctr1 pulses, so changes occur on its edges.

Period is 10 us, pulses and delays are 1-3 us.

06-16-2016 03:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Alexander,

With small modification it's exactly what I'm looking for (digital pulse must be armed on LOW-->HIGH and HIGH-->LOW transition of the analog signal)

Thanks.

06-16-2016 03:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Alexander,

This VI doesn't work - analog pulses aren't generated at all.

Your previous version perfectly matches my case ... altough implemented without any HW trigger.

![digital_pulse_width_modification_issue [0].png digital_pulse_width_modification_issue [0].png](https://forums.ni.com/t5/image/serverpage/image-id/184897i35F5A2BD37235FE5/image-size/original?v=v2&px=-1)

![digital_pulse_width_modification_issue [1].png digital_pulse_width_modification_issue [1].png](https://forums.ni.com/t5/image/serverpage/image-id/184903iFA05CEC03703B870/image-size/original?v=v2&px=-1)

![digital_pulse_width_modification_issue [2].png digital_pulse_width_modification_issue [2].png](https://forums.ni.com/t5/image/serverpage/image-id/184911i0D45073AE5C4B0F7/image-size/original?v=v2&px=-1)

![digital_pulse_width_modification_issue [3].png digital_pulse_width_modification_issue [3].png](https://forums.ni.com/t5/image/serverpage/image-id/184915i52CA2B4335D019F2/image-size/original?v=v2&px=-1)

![digital_pulse_width_modification_issue [4].png digital_pulse_width_modification_issue [4].png](https://forums.ni.com/t5/image/serverpage/image-id/184948iBFB95E4F5068827D/image-size/original?v=v2&px=-1)

![Digital_pulse_followed_by_analog_signal_update [Alexandre_Sobolev].png Digital_pulse_followed_by_analog_signal_update [Alexandre_Sobolev].png](https://forums.ni.com/t5/image/serverpage/image-id/185045i403623094E10B4B5/image-size/original?v=v2&px=-1)