- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Time elapsed between two events in FPGA -

Solved!02-28-2024 06:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

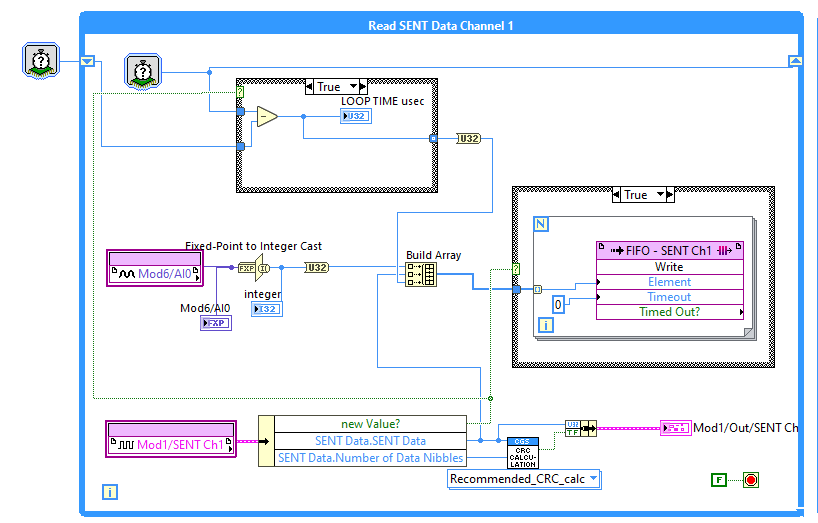

I'm trying to measure elapsed time between two events in FPGA.

My idea is to use Shift Register according well known pattern from NI Courses.

Elapsed Time shall be calculated in microseconds if " New Value " flag is updated from hardware.

The Boolean flag "new Value" is set to true by the LabVIEW Driver when the driver received a new decoded SENT Frame from the Module. This flag is reset during readout. It will stay true as long as the IO Node has not been read out yet.

The SENT data will stay the same until a new Value has been received by the Module.

How to measure time between next " New Value" ?

Thank You for support

Tomasz

Solved! Go to Solution.

- Tags:

- fpga

- Time Counter

02-28-2024 06:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Tomasz,

@Tom_wolf wrote:

How to measure time between next " New Value" ?

So you want to get a "timestamp" (or time-related value) each time you get a rising edge on your "new value" boolean?

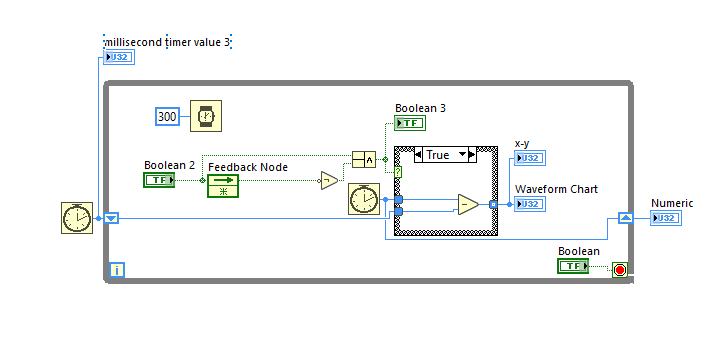

Use a simple boolean operation (with a feedback node) to determine rising edges on your boolean value and then a case structure (and a shift register) to handle your "timestamps"...

02-28-2024 06:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW

So you want to get a "timestamp" (or time-related value) each time you get a rising edge on your "new value" boolean?

--> yes, I would like to have time elapsed between next rising edges of Boolean "New Value".

Use a simple boolean operation (with a feedback node) to determine rising edges on your boolean value and then a case structure (and a shift register) to handle your "timestamps"...

--> Could You propose code fragment with feedback Node - this is little bit mysterious for me especially at FPGA target.

Best regards

Tom

02-28-2024 07:58 AM - edited 02-28-2024 07:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Tom,

@Tom_wolf wrote:

Could You propose code fragment with feedback Node - this is little bit mysterious for me especially at FPGA target.

This code snippet works on FPGA the same way as on Windows computers:

Simple boolean algebra...

02-28-2024 08:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks!

I'm testing now similar code at my PC ( I'm avoiding 10 minutes of compilation 😥) . Looks quite optimistic.

Thank You

Best regards

Tom

02-28-2024 08:54 AM - edited 02-28-2024 08:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Tom,

@Tom_wolf wrote:

Looks quite optimistic.

I don't think you want to feed the current timer value to your shift register in EACH iteration...

@Tom_wolf wrote:

I'm testing now similar code at my PC ( I'm avoiding 10 minutes of compilation 😥)

You know you can run FPGA VIs in simulation mode on your (Windows) computer?

Btw. 10 mins is quite fast for FPGA compilation...

02-28-2024 09:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Tom,

@Tom_wolf wrote:

Looks quite optimistic.

I don't think you want to feed the current timer value to your shift register in EACH iteration...

- What is better option?

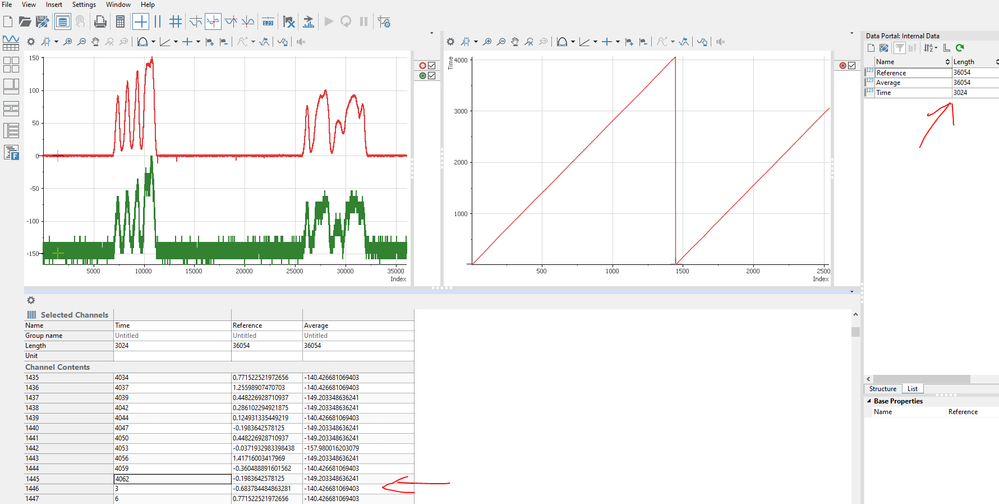

- Look to my FPGA. VI - It calculates 2-3 microseconds if time between rising edges.

- at my Host side I'm logging only a little bit more than 1000 samples for time

- is there any buffer for 1000 samples?

- it looks like time channel is resetting and then starting from 0.

I add my Host and FPGA main files, could You look on it and advise something, please?

You know you can run FPGA VIs in simulation mode on your (Windows) computer?

Btw. 10 mins is quite fast for FPGA compilation...

I Imagine that there are more complicated systems than mine 😁

Tom

02-28-2024 11:17 AM - edited 02-28-2024 11:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Tom,

@Tom_wolf wrote:

I add my Host and FPGA main files, could You look on it and advise something, please?

Attaching FPGA VIs without their project file is quite senseless as all the hardware definitions are lost…

Attaching VIs without all their subVIs is quite senseless as we cannot run them…

Why don't you cleanup your block diagrams? A clean block diagram is much more readable!!!

Suggestion:

You don't need a separate NOT when you use the CompoundArithmetic! You can invert each input and output terminal!

You could use Select instead of a case structure.

You most probably want an ElapsedTime so you need to keep the last "start time" in the shift register!

It doesn't make sense to put indicators at the shift register output (after the loop) when the loop is set to "NEVER stop iterating"...

02-29-2024 04:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello GerdW,

I would like to repent - for this mess in my files and "stalking" You and Your team.

Since this morning I was testing this suggestion - It works as I want

Thank You for great and quick support.

I'm admiring Your and other NI Knights knowledge and experience. From this point I see how many light years ahead of me to reach a portion of Your knowledge.

Thank You

Best regards

Tomasz