- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Transfer 1-d array using DMA FIFO from FPGA

Solved!07-19-2011 04:44 AM - edited 07-19-2011 04:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

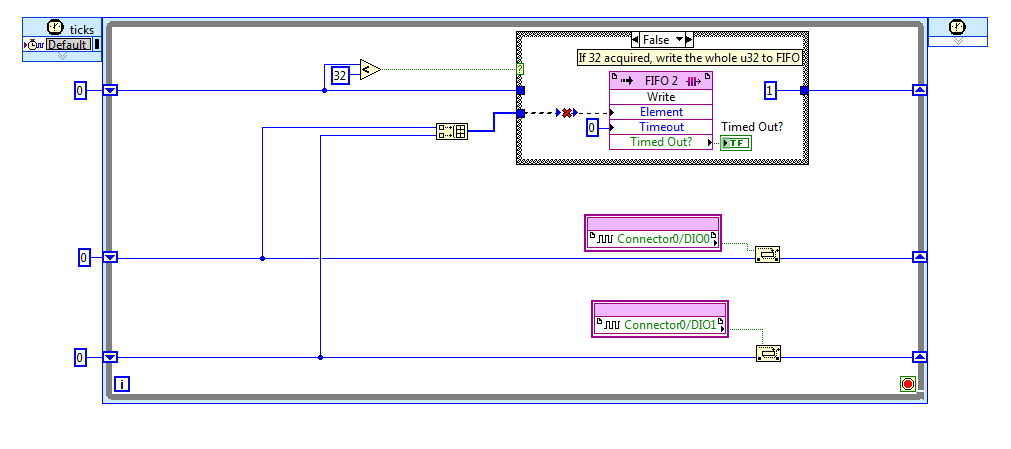

I am trying to transfer a 1-D array of two U32, using a U32 configured FIFO to the host,

but I get error due to connecting to different terminal types,

It looks very simple, I've found many samples around here with very similar treatment, but I can't see the problem?!

Solved! Go to Solution.

- Tags:

- fpga dma fifo array

07-19-2011 04:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The data type of an FPGA FIFO can't be an array, it must be scalar. In your case it's a U32.

And you can only write one element to a FIFO per Write operation. So you'll have to write the data to the FIFO element by element.

07-19-2011 05:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

But in this example:

https://decibel.ni.com/content/docs/DOC-6303

I think FIFO is passing an array, right?

07-19-2011 05:03 AM - edited 07-19-2011 05:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There's a for loop indexing the array... So the write operation is element by element.

The read operation (on the host) can read several elements at a time (--> an array).

07-19-2011 05:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks,

07-19-2011 10:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your response.

But it leads to another question,

How can I transfer several channels in this situation on a Single-Cycle Timed Loop?

I am using Timed Loop because I need to read digital data at high speed up to 40MHz, and because of limits in number of DMAs I need to pass several channels by one FIFO.

07-19-2011 10:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It's quite simple: send one channel per iteration. If you need the sampling of all channels to be synchronous you'll have to store the values in a shift register to send it later.

In the screenshot you posted you could change the code like this (looks like you're using counter values from 1-32):

- when the counter reaches 32, write the data of ch1 to the FIFO and store the value of ch2 into a shift register

- when the counter is at value 1 write the value of ch2 (which was stored in the shift register) to the FIFO

- in all other cases just increase the counter

07-19-2011 11:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks again, for your great help.