- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[cRIO - FPGA] Parallel loops with the same subVI do not run

10-26-2020 09:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

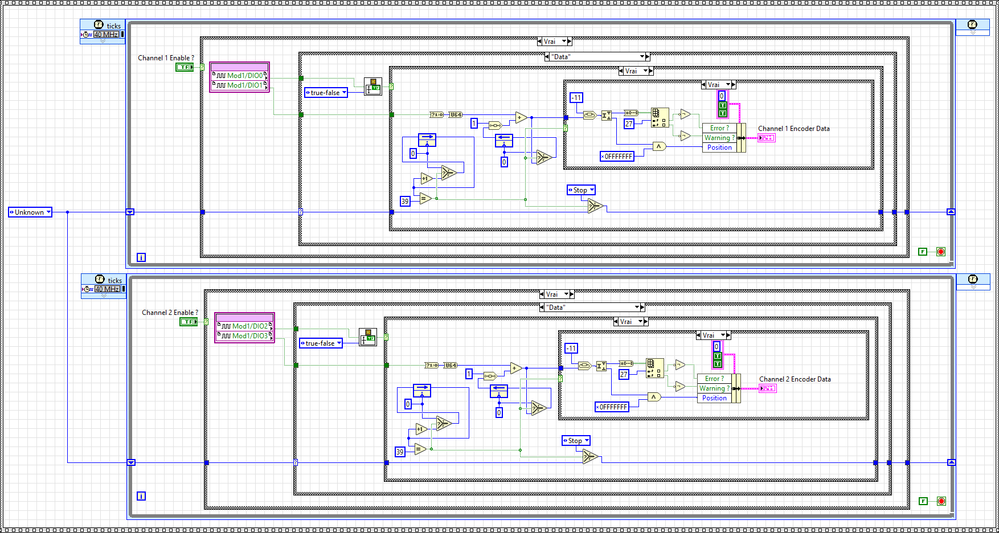

I developed the following LabVIEW code for decoding digital signals from two dual channel on NI 9402 module.

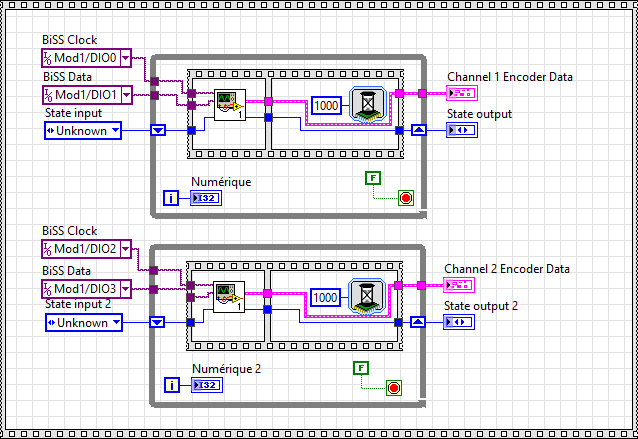

But, when I create a subVI for more readable code (see below), the loops don't want to run them.

Can someone guide me to a solution?

10-26-2020 10:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Eyevolf,

@Eyevolf wrote:

But, when I create a subVI for more readable code (see below), the loops don't want to run them.

What exactly means "don't want to run them"?

Is your FPGA VI broken?

Is the subVI set to reentrant? (Should be on default.)

Mind to attach your project as ZIP?

10-26-2020 11:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello GerdW,

No, main FPGA VI isn't broken, and Yes, the subVI is set reentrant (preallocated clone).

Main FPGA VI can run, but the loops seems to be freezed (no incrementation of "Numerique" and "Numérique 2" and no data).

These VI are in the attached file.

Thanks.

10-26-2020 11:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Eyevolf,

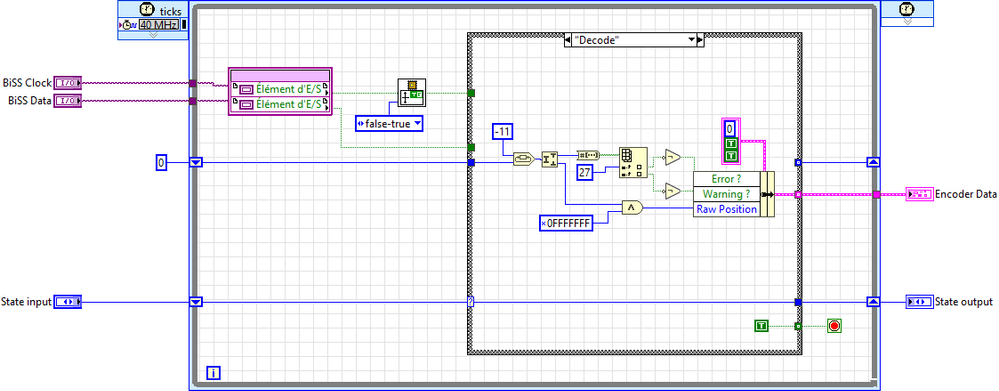

does it work as expected when you create two copies of that subVI, with each copy accessing those DIO pins directly (without using an IO name constant)?

Btw. when dealing with RT/FPGA code it really helps to attach the whole project including the lvproj file!

10-26-2020 11:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You are calling your subvi with the Unknown state on the first iteration. Inside your subvi you have a loop that only exits if the state is Decode. I've not looked at all of the code, but the only other state that you can get to is Idle, which also does not exit the loop. Idle then can only go to Idle or Unknown. You have an infinite loop.

10-28-2020 06:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Indeed, a state is missing and the loop runs indefinitely...

Thanks !