- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

02-03-2015 10:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Mathieu,

Yes, the pictures showed up now. Since the generation appears to be stopping short of completion, I'm curious if we're getting errors somehow from names that we can't differentiate (It appears that the indicators in question have similar names) As a quick test, if you change the names of the outputs causing issues, do they continue to error during generation? It's also interesting that you don't get a log file since the error popup message should be tied to triggering the log generation. In case it was placed somewhere else (somehow), if you search your computer there's no "VeriStand FPGA XML Builder Error.log" on disk?

--Ryan_S

02-03-2015 11:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Names have been renamed by hand for the purpose of taking the screenshot

But you're right, there were initially some duplicate names. Generated code had names like "XXXX 2" for duplicate names, which sounds like it was able to sort that naming issue properly.

Part of the data sent from VeriStand navigates through our LV code and is sent back to VeriStand (due to testing purposes and customer requirements). I had been renaming all those names by hand, so that there was no more duplicate. That was before posting on the forums. Do you think that the node could somehow be broken and that it would be of interest to restart from scratch and take care of names in order to never have the node try working with duplicate names ?

The error file is usually located in the same folder than the generated code + png. I had been removing by hand all those files before trying to generate the code this time. The error file doesn't show up in the directory, and a search for it on my HD dones't return any match

Thanks for your help

02-04-2015 03:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ryan,

As an update.

I deleted the node, and created a new one, fro, scratch. Wired all inputs, then created all outputs by hand, making sure to not duplicate any name.

I couldn't reproduce yesterday's error.

I guess that my node went corrupted at some point.

We are still experiencing issues with the generated fpgaconfig:

- all scales are set to 1

- fpgaconfig file is using locale settings, which means that decimal separator is a "," in the fpgaconfig file. VeriStand doesn't allow us to import a fpgaconfig file formatted this way. One has to change all "," into ".". I guess that could be fix on your side by asking the code to not use the locale setting for decimal separator

Thanks

02-04-2015 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ryan,

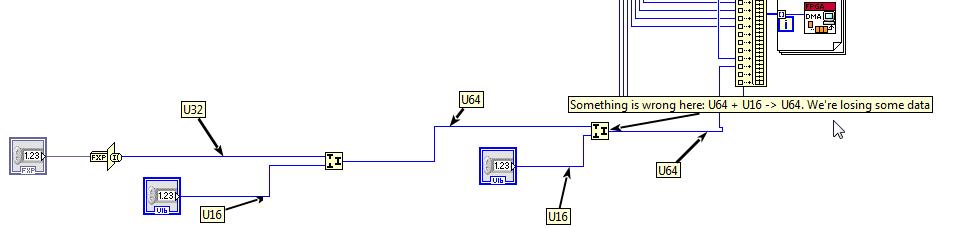

We were wondering why our FPGA code was working while we couldn't have it work when targetted from VS with the FPGA XML builder node. We just understood that there are casting issues that appear when you start using u8, i8, u16 or i16 mixed with FXP for example (in our case). Here is an example of code generated

For part of our project, we're forced to move back to manual design.

Cheers

02-04-2015 10:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Matt,

Several items to cover here:

1. With regards to the duplicate names, VeriStand does not allow for inputs or outputs in the same hierarchy to have the same name so I initially implemented the controls/indicators internal to the node to have just the name of the input/output. However, this then doesn't cover the case where you have an inputs and/or outputs of the same name in different hierarchies, which VeriStand would support and I'm guessing was the case in your system (i.e. Inputs\MyChannel and Inputs\Folder\MyChannel). This is a bug with the node. To workaround it, as you've found, you'll need to keep everything with a unique name.

2. As to the settings from the new node:

2.1. I understand that a default of 1 doesn't work for scenarios outside of FXP and PWM. We do recognize this as an issue/shortcoming.

2.2. I know the period versus comma issue, based on the default delimiter of your OS, has come up before and does cause issues loading the file until they're replaced with periods.

3. I was aware of bitpacking issues with FXP datatypes below 32 bits when packed with numerics below 32 bits, but I believed this was resolved in 1.1.1. I believe you previously mentioned being on 1.1.1, but can you confirm you're on this latest release? If the bitpacking is in fact still packing improperly, you would need to move back to manual design, for now, as you've done.

--Ryan_S

02-04-2015 10:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ryan,

VIPM states I'm using version 1.1.1.41

Cheers

02-04-2015 10:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I thought 1.1.0 and later had loop unrolling? The screenshot has the DMA loop still

02-04-2015 10:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Stephen,

1.1.0 and later does unroll the DMA from VeriStand, but the DMA writes up to VeriStand are still done with the For-Loop. The backend logic for unrolling this second DMA is similar, but hasn't been implemented.

Thanks! --Ryan_S

07-08-2015 12:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Eric.M,

The issue with commas verus a period as the decimal mark on non-English operating systems has been fixed in release 1.1.2 of the add-on.

--Ryan_S

09-17-2015 09:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I use this great tool and it really eases the fpga development for Veristand.

But I think there is a lack in the use of the node: I would like that the channel index can be changed.

Sometime, the position of the data makes the wiring in block diagram less readable and I expect to change the inputs/outputs order.

So is it possible to add this modification for the next release ?

Best regards