- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

03-19-2016 12:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I'm working on HIL system, and we need to simulate some sensors using PWM Out channel, but we have to change the duty cycle and frequency of the PWM Out channel at runt ime, so is there any good solution for us to add both of the duty cycle and frequency items for PWM Out channel in Veristand FPGA XML Builder Node? Same questions to PWM In channel.

Thanks

04-01-2016 05:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey EricNe,

Appologies for the delay in response. From looking at the VI, I don't think you're doing anything wrong, looks like a bug in how we're handling the code generation for only boolean outputs. If you add a dummy U8 output to the bottom of the node it should build properly. You'll have an extra U8 channel in VeriStand, but it's a simple workaround to get the generation to work.

Let me know if that works for you and if you have other questions.

Thanks! --Ryan_S

04-01-2016 05:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey huazy,

Appologies for the delayed response. Using VeriStand's default PWM packet, you define the period as a static setting in the XML via the PWMPeriod tag. Within the FPGA XML node, you set this via the "Default PWM Period (Ticks)" setting.

The channel you then get in VeriStand is a duty cycle channel, which based on user input, varies the high and low times written to the FPGA and used to output the DIO line.

Now, if you want to control both frequency and duty cycle on the fly, this is totally doable and is an intended use-case. The RIO library functions that install with the VeriStand FPGA template include VIs and XML declarations to use the default PWM channel as well as control both frequency and duty cycle directly (See NI VeriStand RIO Library\IP Based IO\Pulse Generation\1 PulseGeneration.vi)

You do this by passing both high and low time yourself. So, to generate a PWM where you control frequency and duty cycle you would pass two U32 channels to the FPGA and they would represent high time and low time. You can use the scaling to convert from seconds, ms, etc into FPGA ticks. So, using the RIO Library and the FPGA XML node it would look something like this (for PWM generation):

As for scaling of the U32 channels, it depends on what you want your inputs to be. If you do it in time (seconds, etc) then you could scale that to FPGA ticks easily enough. Or you could have a model or something like that running the calculation and feed it down to the FPGA already in ticks. Developer's choice.

Hopefully that answers your question. Let me know if there's any other details you're curious on.

Thanks! --Ryan_S

04-15-2016 02:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This add-on is very useful but I found a problem (bug?).

It seems that splitting the data written by VeriStand is incorrect.

I want to send reproducible code to you.

Would you contact me by e-mail?

Thanks,

Yusuke Tochigi

05-01-2016 09:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have found a workaround so, Im creating a document for this issue.

05-19-2016 05:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ytochigi,

Can you post your document for this issue?

Thanks!

05-19-2016 07:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Joshe, yes I have already created the document, but it is written in Japanese....

I believe it should be translated into English so give me a time please.

06-17-2016 11:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

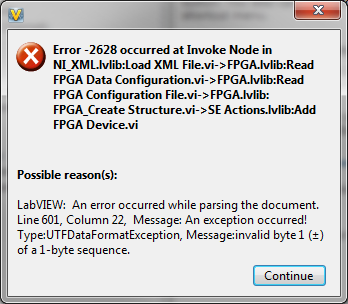

I have had success using this add on in the past, but am getting this error message when I try to import the FPGA into VeriStand. Any ideas? I have looked at the error line in the .fpgaconfig file and it looks fine. I am using VS 2015 and LV 2015 sp1. I can upload the project if need be.

Thanks,

Josh

06-19-2016 09:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Joshe,

Nothing jumped out at me from the XML snippet and error. I'm wondering if it's a red herring propogating from an upstream error.

Can you upload the full XML file and FPGA VI? For the VI all we really need is the configured node, so you can delete any other IP if needed. That should let us take a closer look at what's going on.

--Ryan_S

06-27-2016 09:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ryan,

Sorry not to respond sooner, I was out of town. Here is the XML and FPGA VI. Thanks!!

Josh