- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Calculating apparent, real, and reactive power with three phase voltage and current inputs

11-08-2013 02:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

I am new in using labview FPGA for power measurements. May be the solution for this question already exist. I looked at some of the pre existing codes. Seems like the data will be streamed to the host and then the host will analyze the data.

I want to make the all the calculations in the FPGA and make the host just display the data. I need this because, the RS 232 and the ethernet in the sbrio 9642 sends and receives data. This takes a lot of room in the host and I want to move th real, apparent and reactive power into the FPGA.

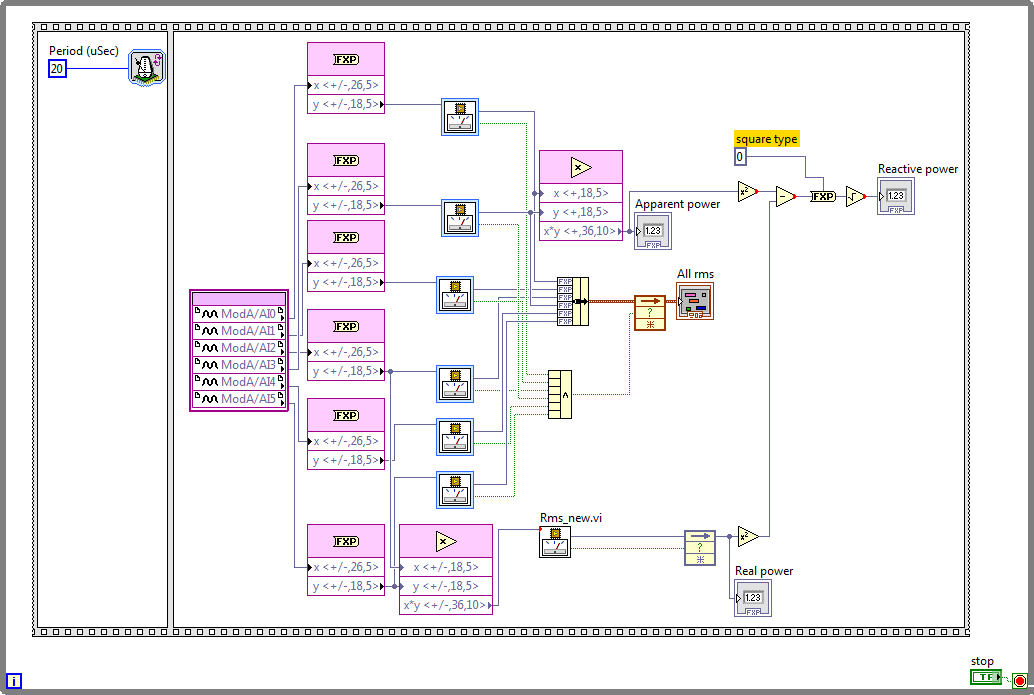

1. Apparent power:

The apparent power calculation was quite simple. I multiply the rms values of current and voltage. This product is then multiplied with 3, since it is a three phase.

2. Real power:

For the real power, I multiply the instantaneous value of the voltage and current (VI), this product is fed into the modified RMS block. In the modified rms block, I removed the square component to obtain the integral of just the VI values instead of the square of VI.

3. Reactive power:

For the reactive power it is simple. I use the apparent and real power and use the following equation

Reactive power = square root( apparent power^2 - real power^2)

I have attached my present code with this. I have modified the rms block to calculate the real power. Basically, I removed the square component of the rms.

The apparent power calculation and the reactive power calculations are very straight forward. But, I am trouble with the real power calculation. It would be great, if some one can take a look at the code I have attached and let me know, if this can work. I see red dots at the square block and the square root block. even though this did not generate any error. I would like this issue to be avoided.

- Tags:

- fpga

11-11-2013

02:28 PM

- last edited on

05-10-2024

08:46 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Most of your code was correct except that the real power is the mean/average value of the instantaneous power. Therefore you should use the mean subVI rather than your modified RMS subVI for that calculation. Here are the formulas you want to use.

Real Power (P) = Avg of Instantaneous Power

Apparent Power (S) = Vrms * Irms

Reactive Power (Q) = SQRT (S^2 - P^2)

Power Factor = P/S,[-1, 1]

For a floating point IP core to testbench against, I used the NI LabVIEW Electrical Power Suite (https://www.ni.com/en-us/shop/product/labview-electrical-power-toolkit.html). Here is a screenshot of the subVI that does these calculations.

Note: The identity of the analog input channels was not clear in your application. I assumed they are in this order: voltage A, current A, voltage B, current B, voltage C, current C. If that's the case, the wire going into the multiply operation for the real power calculation was miswired. Depending on your physical wiring of the I/O channels, you may need to change it back.

To test the FPGA code for calculating the power values, I used the new Desktop Execution Node (DEN) feature in LabVIEW 2013. This enabled me to testbench the FPGA code against the floating point values calculated by the LabVIEW Electrical Power Suite, as shown below. You can see that after fixing the FPGA code, the calculations match.

Note that in the top right corner of the testbench VI, the floating point results from the LabVIEW Electrical Power Suite are compared to the fixed-point FPGA calculations. You can see that they match fairly well. Also note that I added a power factor calculation to the application.

![[Testbench] FPGA Power Measurements - FP.png](http://forums.ni.com/legacyfs/online/134469_[Testbench] FPGA Power Measurements - FP.png)

Note that due to the pipelining delays in the FPGA application, I play the same power waveforms twice-- thus the outer For Loop.

![[Testbench] FPGA Power Measurements - BD.png](http://forums.ni.com/legacyfs/online/134470_[Testbench] FPGA Power Measurements - BD.png)

The configuration of the Desktop Execution Node is shown below. Note that Clock Ticks is set to 800 ticks (25 nanoseconds per tick) to match the 20 microsecond timing of the FPGA while loop (below).

Note that while running pre-compile simulations with the Desktop Execution Node, you have full debugging capability on the FPGA application (highlight execution, probes, breakpoints, etc.). Here is the updated FPGA application.

![[FPGA] FPGA Power Measurements - BD.png](http://forums.ni.com/legacyfs/online/134472_[FPGA] FPGA Power Measurements - BD.png)

![[FPGA] FPGA Power Measurements - FP.png](http://forums.ni.com/legacyfs/online/134473_[FPGA] FPGA Power Measurements - FP.png)

To switch between pre-compile simulation mode and compiled deployment to the FPGA, right-click on the FPGA target in the LabVIEW project.

Additional Notes:

- Note that I didn't spend any time adjusting fixed point word lengths. Most likely shorter word lengths could be used that give comparable accuracy.

- Also take a look at the internal configuration of the RMS and mean functions. The loop rate is set to 20 microseconds, but the internal configuration of the FPGA IP cores does not match. I didn't change these internal configurations.

11-12-2013 01:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brian,

Thank you for your message. I tried the real power calculation you have shown and I am getting good results.

Also, I learned how to use desktop execution node from your discussions.

- Kumar

11-01-2018 02:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi..

hope this works with sinusoidal voltage and current wave forms where frequency remains constant.

Suppose the line frequency is 50 Hz and the sampling rate is 50000 samples per second per channel.so number of samples per cycle is 50000/50 that is 1000 samples per cycle.The RMS calculation for cycle gives correct results.

But if there is change in frequency suppose frequency changes to 49.5 Hz.So number of samples per cycle is 50000/49.5 that is 1010.Calculating RMS by 1000 samples instead of 1010 gives some error.

Better results yield with windowing 'N' samples > FFT (single Side) to calculate the power parameters such as RMS,Power factor,Apparent power,Real Power,Frequency etc.