- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Help on discrete controller design for DC-DC converter in FPGA target

10-16-2018 05:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi guys! I am new to program design using FPGA, and I meet some probelms in experiment. Hope to get some help from you and thank you very much.

I want to design a digital signal processing (DSP) algorithm in FPGA target using myRIO for the control of DC-DC converter, and in my system the sampling frequency is 10khz. Because of the limited resource of FPGA in myRIO, I use FPGA IP to design digital algorithm which is using fixed-point signal and working with single-cycle Timed Loops. However, the sampling frequency I set for my experiment is 10khz, which is realized in while loops using loop timer. And the IP builder generated vi must be utilized in single-cycle timed loop. I tried to insert a single-cycle timed loop with 40Mhz into one while loop with 10khz to design the program, but failed.

I am very confuded about the design thougth about my situation. Can you give me some help and advise about digital signal processing (DSP) algorithm using FPGA with fixed sampling frequency? Thank you very much.

10-16-2018 06:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Hibo,

I don't know how to help you on your problem, but I will be working on controlling a DC DC converter using GPIC. So i wonder what is the model of the converter that you are working with?

Hope you'll find a solution soon.

10-16-2018 07:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear REaymane:

Thanks for your reply!

The model of the converter you mentioned is the converter type? At present, I firstly study the digital signal processing (DSP) algorithm design for basic DC-DC buck converter using FPGA. Later, I will go on for other DC-DC converters, such as DC-DC boost converter, bidirectional DC-DC converter and so on.

I have read some study materials about GPIC, but still I am confused how to design. I think my design though for controlling a DC-DC converter using FPGA is not clear (which is the best way?), so could you please give me some advises? Is the GPIC the better way for controller algorithm design?

Looking forward to your reply!

10-27-2018 02:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

We are also working on DC-DC converter design controlled with an sbRIO 9637. Our challenge is that we need to interleave 6 channels. We are interested in collaborating on the program if other people will help with the code.

Currently we have the core VI operating on the FPGA that operates at a clock frequency of 240MHz. This VI outputs 6 digital outputs that will drive the six half bridges. Each half bridge is expected to have its own gate drive IC that generates a complimentary signal with a fixed dead time. We are pushing the clock speed as high as possible so that our target a switching frequency of 200kHz, we still have good resolution.

This code responds to an externally provided base duty cycle and then a duty cycle correction value for each of the 6 individual phases using an independent current reading on each phase.

We have just started looking at integrating a PID loop on the real time level to update the duty cycle value and the 6 phase corrections per 6 current sensors that measure each phase and one main current sensor that measures total current flow. This is where we could use some help.

For the GPIC program, does your GPIC have a 9606 or a 9607 sbRIO. For the cRIO rack, what model number are you using.

Our VI using the variable depth RAM FIFO currently is compiled on the Zylinc 7020 right now, you'd have to experiment if you can get it working on the older Spartan FPGA and it may need a reduced clock speed. If you are not switching about 100kHz this will not be a problem. We're still optimizing the code to get the SCTL clock speed to 300MHz.

Dave

10-27-2018 02:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

One other comment, we're using LabVIEW 2016 because that is the last version we have the power electronics tool kit for.

10-27-2018 10:08 PM - edited 10-27-2018 10:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Dave@RPS:

Thanks for your reply!

My NI device for experiment available now is myRIO 1900 with a clock frequency of 40MHz. And for GPIC program I don't have 9606 and 9607 sbRIO.

Now, voltage control loop is utilized to stabilize the opearting system in our system. Whether it is current control or voltage control, both are designed for duty cycle reguration to obtain stable output voltage. And is the problem you meet the current control problem?

We have finished the PID control and another digital control algorithm using GPIC in while loops and the sampling frequency used for digital control design is 10khz. However, the limited slice resource (4400 slices of myRIO 1900) is the main problem for us to complete much more complex digital controller. I have a doubt that if we use SCTL, it is possible to design complex discrete control algorithm running in the while loop with 10khz sampling frequency? The reason we want to use SCTL is to save resource. Is it possiple?

Hope to talk more about this issue with you.

Best regards

Hibo

10-29-2018 02:32 PM - edited 10-29-2018 02:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hibo

It sounds like you only have a myRIO or do you also have a GPIC set?

The myRIO's are limited in resources; the sbRIO 9607 which comes with the NI GPIC kit or the sbRIO 9637 that comes with a RIO Eval kit may give you the added resources you need.

We are doing this in spurts, first we figured out how to interleave and drive the PWMs at higher speeds, then we will tackle the control code. We're focusing on other projects right now, we'll pick back up on the control programming in a few weeks.

Dave

10-29-2018 07:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dave@RPS

At present for practice, I only have myRIO for experiment. As you mentioned, the limited resources is a big problem for us now. We need more resource for control algorithm design and we are considering buying another NI FPGA device for experiment, as you recommended, sbRIO 9607 is a good choice.

Hope your project goes well.

Hibo

11-07-2018 05:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hope this will help. We are currently using the PEB-Board system for controlling power electronics converters. Being based on the NI sbRIO-9651 you can use LabVIEW. Sample programs are available on the website. www.ped-board.com

11-07-2018 11:53 AM - edited 11-07-2018 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I just looked again at the PEB system, it looks like a great compromise between performance and cost as you grow a power electronics program. When we get further along I'll look more into the PEB system as its evolved a lot since I first looked at it.

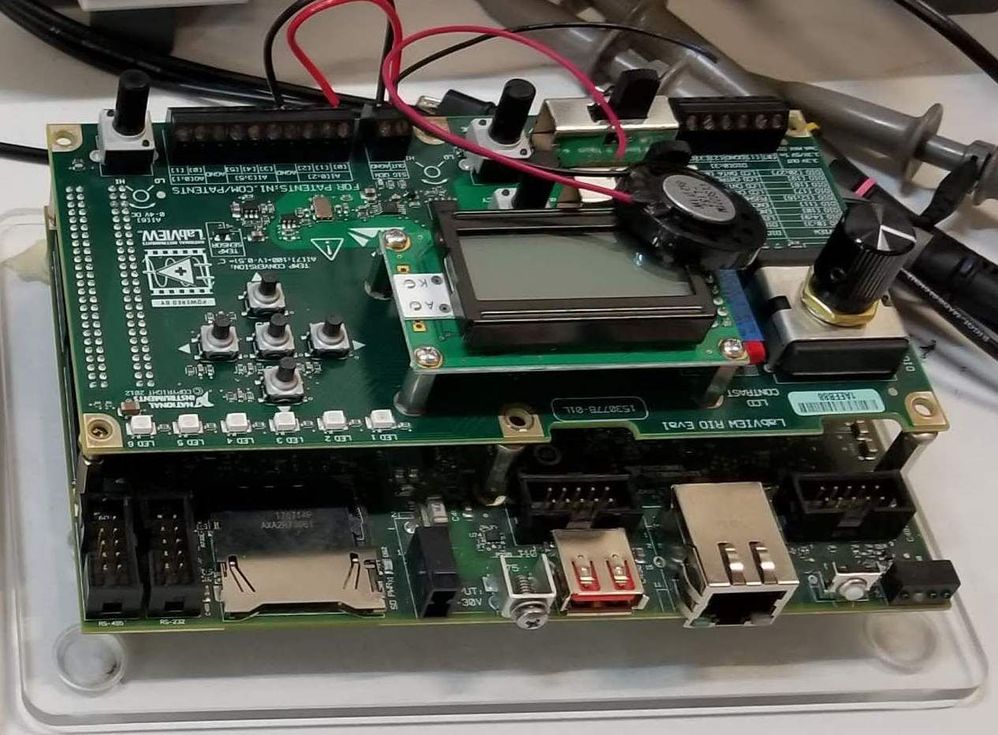

A more economical but less flexible option you should consider at the very beginning of your FPGA and power electronics development program is buying a RIO Eval kit. They cost $466 and you can only purchase one of these for training, but it comes with a tutorial project mezzanine board on top of an sbRIO 9637. This mezzanine board is great for learning to use the sbRIO, and has a bunch of switches, and encoder, LED's. It also serves as a limited breakout board with access to four FPGA DIO, a signal generator (square, sine, triangle waveforms) and six 16 bit analog inputs and 4 outputs, all +/1 10 Volts. The picture below shows the tutorial mezzanine card on the sbRIO

We've made a breakout PCB board for the sbRIO9637 that allow access to all 16 analog inputs, 4 analog outputs and 28 FPGA DIO. A picture of it is shown below. The minimum batch of these was 5 and we have 3 extra's that we'll trade with people who don't mind the hole mismatch on this first batch.