- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MyRio analog input

08-09-2014 12:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Greetings,

I am new to NI and I have a question about the setting the timing on the analog inputs. I want to set up a clock (DIO output) and in addition, have ever clock rising edge initiate a single A/D conversion. Is this possible with the MyRio?

The background is I have a device with a string of sensors that will output a analog value every time I send in a clock, therefore I need to digitize the analog signal synchronized with the clock.

In addition, if someone has found documentation other than the manual, I would appreciate your sharing.

Thanks for the help,

Frank

08-11-2014 10:10 AM - edited 08-11-2014 10:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Frank,

Welcome to the forums! What you want to do is definitely possible with the myRIO. You have a few options available to you:

If you have the ability to upgrade to LabVIEW 2014, the myRIO 2014 toolkit includes new Interrupt Express VIs. You specify a condition (in your case, a rising digital edge) and a callback VI that executes when this condition is met. The best way to learn about how this works is to take a look at the examples in Example Finder (Help»Find Examples»Toolkits and Modules»myRIO»Interrupt Handling.lvproj.

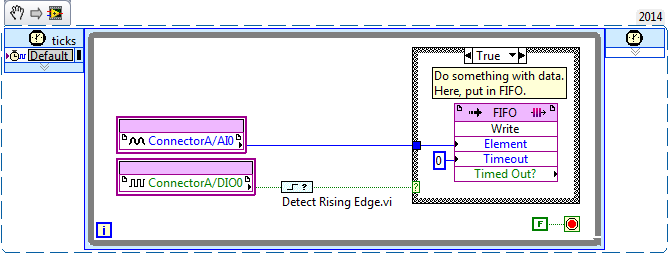

If you don't have the ability to upgrade to LabVIEW 2014, you could implement something similar yourself by having a loop wait for a rising edge on a digital line by using the Digital Input Express VI and then doing the analog measurement. This method would introduce some jitter because of the overhead associated with the Express VIs. An example snippet of this is below. If you do have access to the FPGA module, I would recommend implementing this logic on the FPGA instead (further below).

Using the FPGA module to do the triggering would give you better results because of the tighter timing capabilites of the FPGA as compared to the Express VIs. The logic would be mostly the same on the FPGA as it is on the real-time except for the appropriate VIs swapped around:

Here, we are waiting for a rising edge on a digital line and then placing the data from the analog channel in a to provide this data to the host (real-time) application.

If you want absolute control over the synchronization of the AI to the clock, I would recommend implementing the logic in FPGA (2013 or 2014). If your application has a little leeway in terms of timing, the Express VIs (2013) or Interrupt Express VIs (2014) would work for you.

Let us know if you have any questions!

Best Regards,

Offering Manager

NI

08-11-2014 10:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Matthew,

This is really good news! I will try this out today and let you know how things work out.

Do you have an estimate of how fast these loops can execute (Samples/Sec) on the MyRio?

Thanks again,

Frank

08-12-2014 08:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Frank,

On the FPGA, you should be able to achieve a loop rate of up to 40 MHz. On real-time, it's a little more difficult to estimate as I've never benchmarked it but I think 1 kHz would be a good estimate for a starting point. One of the nice things about timed loops is that you can tell if the loop finishes late so you can adjust the timing.

Best Regards,

Offering Manager

NI

09-30-2014 08:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Matthew-B,

Sorry to dig up an old thread.

I'm new to myRIO and the ZYNQ line so bear with me. I'm curious as to why you estimate that you could only get 1kHz loop rate on real time. The processor is running very fast (I don't remember the exact rate, but I think it was hundreds of MHz)...shouldn't I be able to easily get into the tens or hundreds of kHz loop rates with real time?

Just from reading the myRIO specs, I was hoping to be able to run a timed loop at 96kHz to sample an analog input without having to reprogram the fpga. Is this not possible? Writing fpga code is not a problem, I was just hoping to save on compile times while in the developement stages.

Thanks.

10-01-2014 05:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey my_dubs,

Although I can't speak specifically to what Matthew-B was referencing, I can point you to items that can help you.

With the release of LabVIEW 2014, we also brought something out regarding HighThroughput on the MyRIO. As long as you are using LabVIEW 2014, this should be able to get you where you need.

The NI LabVIEW High-Performance FPGA Developer's Guide

http://www.ni.com/tutorial/14600/en/

NI High Throughput Add-on for myRIO 2014 http://www.ni.com/download/ni-myrio-software--2014/4938/en/ Hope this helps!

10-01-2014 08:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks Douglas,

I'll check out these links and report back!

I am using 2014.

Matt

02-21-2016 05:33 AM - edited 02-21-2016 05:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Matthew,

I'm unable to locate this "Detect Rising Edge.vi" for triggering analog input in FPGA. Can you tell how to find/get this function?