- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA onboard clock stability

Solved!12-20-2015 08:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I'm looking for details on onboard clock stability for cRIOs (mainly 9076). Datasheet does not tell much in this. So what kind of oscillator is used for the onboard (40MHz) clock generation, what accuracy does it have? Without this information I don't see how for example, generated signal timing accuracy can be determined.

Thank you

Solved! Go to Solution.

12-24-2015 04:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

12-28-2015 03:44 AM - edited 12-28-2015 03:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear saimot,

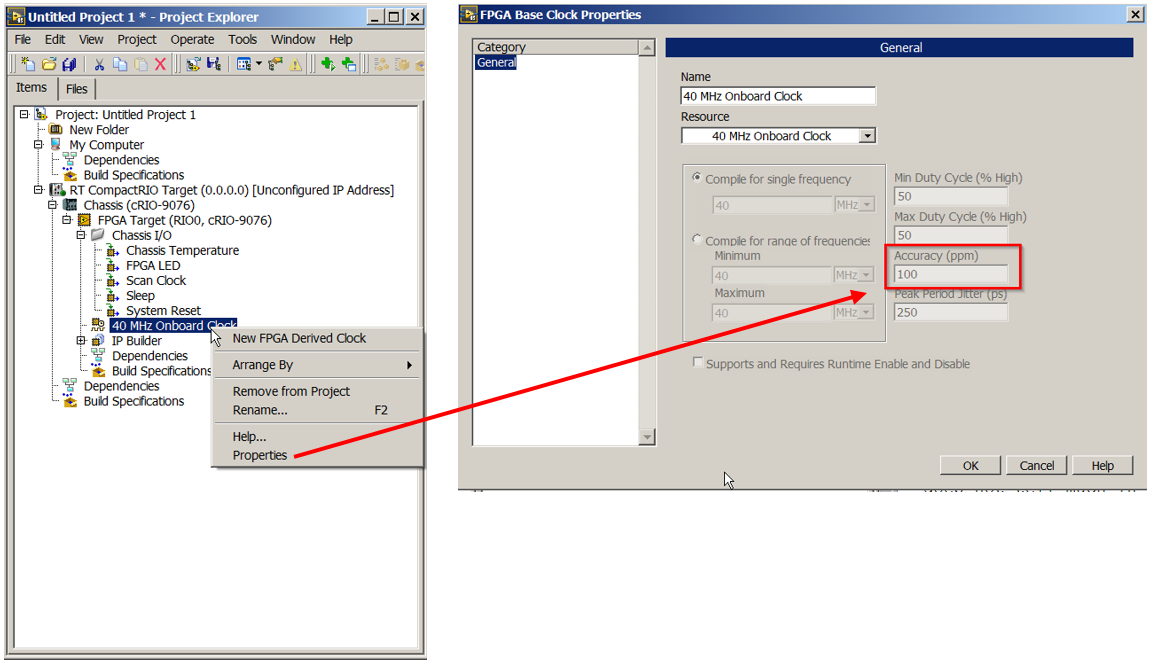

for each clock of the target (the 40MHz onboard and some derived clocks - if the target permits and you created them) you can find its accuracy in the project explorer by right click on the desired clock and selecting properties. See attached picture. Is this the answer for your question?

B/R

12-29-2015 11:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for relpies,

Dennis, since Xilinx manufactures only the FPGA used in cRIO, they re datasheets describe just capabilities and some performance limits of the FPGA chip. Also even within the FPGA chip itself, different peripherals have diffetrent timing performance so the resullting max clock, skew and other parameters are dependent on used resources for the particular application. However, the question I was interested in was the oscillator that NI uses to clock this FPGA (and other resources) in the cRIO.

Jozef, yes I was interested in these number. Chassis datasheet mention just the Internal Real-Time Clock with accuracy of 200ppm (35ppm at 25degC). Therefore I understand the clock that drives the FPGA Base Clock is a different one then the one which RT uses.

Best regards,

Tomas