- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with FPGA configuration in DCAF

Solved!06-22-2018 05:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, I've been trying out DCAF, and I am having trouble getting the FPGA module to work. I compiled a simple FPGA program that allow me to turn on/off the FPGA LED, as well as setting four voltage outputs to an analog output module. The FPGA by itself runs fine, and the bitfile been flashed into memory.

I decided to only have one engine on the cRIO in my DCAF editor, which contains an FPGA Module configuration and a UI Reference configuration. My main vi for the cRIO is similar to the "cRIO Main.vi" in the Temperature controller example, and I used the editor to generate my includes.vi. My user interface is called "Test UI.vi"

I added the *.pcfg file to the cRIO at /home/lvuser/natinst/bin/TestSystem.pcfg

When I run the main vi, I get an error:

Error 7 occurred at NISE_error generator.vi

Possible reason(s):

LabVIEW: File not found. The file might be in a different location or deleted. Use the command prompt or the file explorer to verify that the path is correct.

=========================

NI-488: Nonexistent GPIB interface.

/TestBench_FPGATarget_FPGATest_a8r3rSxImxM.lvbitx

I don't understand what the error means, as I am not using the GPIB interface, but I do recognize the bitfile name used in the FPGA.

What am I doing wrong?

Regards,

Linus

Solved! Go to Solution.

06-25-2018 03:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

07-16-2018 03:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

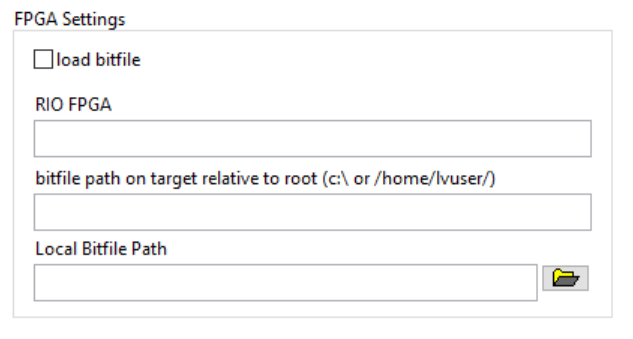

The local bitfile path is S:\LabView\2014 SP1\Test Bench\FPGA Bitfiles\TestBench_FPGATarget_FPGATest_a8r3rSxImxM.lvbitx

07-23-2018 04:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This isn't a module I've used myself but here are some of my thoughts.

1. The bitfile path under FPGA settings should be relative to the root folder so I would not think your path is valid. For starters, I would suggest just setting the bitfile path to FPGA file name "TestBench_FPGATarget_FPGATest_a8r3rSxImxM.lvbitx".

2. This is something that I'm not totally sure about but even if you have the FPGA bitfile in flash I believe you will have to check load bitfile so the engine knows about the bitfile.

3. When you use the deploy tool, is the lvbitx being included? This should deploy the bitfile to the "bitfile path" that you specified earlier so I would make sure the deploy tool is including that bitfile and open an FTP connection to verify that the bitfile was deployed to the correct location.

07-25-2018 09:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear All,

I've exactly the same problem described by ilnus (begging of thread).

I can give you my answers (see below):

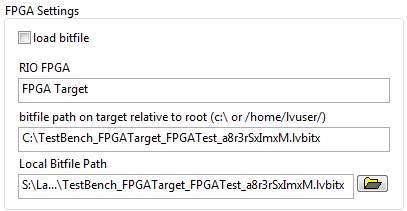

1. The bitfile path under FPGA settings should be relative to the root folder so I would not think your path is valid. For starters, I would suggest just setting the bitfile path to FPGA file name - done (in my case: mani.lvbitx)

2. This is something that I'm not totally sure about but even if you have the FPGA bitfile in flash I believe you will have to check load bitfile so the engine knows about the bitfile. - done; the bitfile is present on the cRIO target and it is not flashed.

3. When you use the deploy tool, is the lvbitx being included? - Yes it is included.

This should deploy the bitfile to the "bitfile path" that you specified earlier so I would make sure the deploy tool is including that bitfile and open an FTP connection to verify that the bitfile was deployed to the correct location.

The bit file is on cRIO in the /home/lvuser/.

My settings are:

07-25-2018 03:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

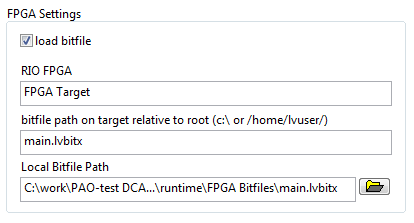

Okay was able to set up a simple test here and dig into the code. It looks like this is a bug that has been reported before and is the result of the target configuration storing the bitfile path as a path type in it's private data rather than as a string. This means that main.lvbitx ends up getting stored as /main.lvbitx and when we build a path with that value as the name/relative path input it results in <Not a Path>.

https://github.com/LabVIEW-DCAF/TagEditorCore/issues/321

Since more people are running into this, I'll see if we can try to get a decent fix although I think the fix would have to involve changing the data type of private data which I'm hoping won't result in other errors.

The good news is that before DCAF attempts to use your path output as a relative path to add on to /home/lvuser, it sees if the bitfile path is a valid file and uses that if it is. This means if you change the "bitfile path on target relative to root" to the full path /home/lvuser/main.lvbitx, it should be able to load that correctly.

07-25-2018 06:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I still have a problem. When I input the full path "/home/lvuser/main.lvbitx" in the bitfile path on target relative to root (without quotes), it automatically changes to "home:\lvuser\main.lvbitx" (without quotes). I don't know if it's just me, or if other people have this issue.

If I run the program with just "main.lvbitx" (without quotes) in the bitfile path on target relative to root, I get Error 7 occured at NISE_error generator.vi. Possible reasons(s): LabVIEW: File Not found.

If I run the program with "home:\lvuser\main.lvbitx" (without quotes), I get Error -63192 occured at Open Dynamic Bitfile References in FPGA manager.lvlib:FPGA manger.vi-> .... ->Host Main.vi Possible reasons(s)" NI-RIO: (Hex 0xFFFF0928) EIther the supplied resource name is invalid as a RIO resource name, or the device was not found.

I always deploy the code with the Deploy Tool before running the vi.

In the DCAF editor, do I need to fill the input box under cRIO Target >> Configuration >>FPGA Settings>> RIO FPGA?

07-25-2018 09:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tomorrow I can post screenshots and configurations of what I have on my development computer which was working but can you let me know what version of LabVIEW and DCAF Core you are using? I'm not sure if any relevant code was changed in recent packages but it would be good to know.

07-26-2018 09:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am using LabVIEW 2014 SP1 with DCAF Core 1.3.0.12 and DCAF FPGA Module 1.1.1.11.

07-26-2018 09:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would recommend keeping the path "home:\lvuser\main.lvbitx" even if it doesn't look correct. The behavior is undesirable, and is again the result of having the bitfile stored as a path data type rather than a string, but because this path is flattened/unflattened using the "path to array of strings" and "array of strings to path" primitives the path "home:\lvuser\main.lvbitx" will end up flattening/unflattening correctly because it is an absolute path.

I think the error you are running into now is due to you specifying the RIO FPGA as "FPGA Target" which is probably the name of the FPGA in your project but not the RIO resource name. In your project, right click the FPGA Target and under Properties look for the Resource which is probably just "RIO0" and try that as the RIO FPGA value.