- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sb-RIO9651 socketed CLIP

Solved!01-03-2018 12:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am trying to find information on using a socketed CLIP on the NI-SOM. The only information I find is how to use the Clip generator to create a clip. But I want to integrate some IP into the FPGA that uses the FPGA IO, and from what I have seen you need to use a socketed clip.

Is importing IP that uses the FPGA IO (a socketed clip) possible on the 9651? Is there any documentation on how to do this?

Thank you.

Certified LabVIEW Architect

Solved! Go to Solution.

01-03-2018 05:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brad,

Yes, a socketed CLIP is in fact the only way to interact with IO on the FPGA with the 9651. The easiest way to implement a socketed CLIP is to use the CLIP generator. You can import this generated CLIP as-is by right-clicking the "sbRIO-9651 Socket" and going to properties. This will import IO nodes which can then be used in a FPGA VI.

Additionally, if you want to further customize your socketed CLIP you can edit the files outputted by the CLIP generator.

This powerpoint is a good guide to creating a socketed CLIP with the CLIP generator:

Best,

Will

National Instruments

01-03-2018 05:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

At a high level, the process is to use the CLIP generator to create the framework or skeleton of a socketed CLIP for the sbRIO-9651, then you can customize or modify that CLIP to add your own IP, including IP that directly accesses the FPGA IO. The sbRIO-9651 uses the CLIP generator because it makes customizing the FPGA IO more user friendly for non-HDL experts, but also exposes the editable source HDL for the IO for advanced users to make low-level and high-performance optimizations.

For documentation and resources, I'll point you to a couple places to get started and get support.

- Hardware Developers Community - this list of resources for SOM covers a lot of the into to custom hardware and digital design needed to support a SOM developer. In addition, there is a dedicated forum in this community with some hardware and FPGA specific experts at NI available.

- From the community, this NIWeek presentation covers the overall development process step by step. It generally avoids the specifics of HDL design, but does mention when you would take that on.

- Specific to CLIP customization, the CLIP Generator Help has a step that discusses how to make changes to the CLIP that would include custom IP. This is called out in the help as well, but be aware that if you customize a CLIP, and then try to modify it with the CLIP generator, the generator will overwrite your customizations, so be careful with your process and source code control to ensure you maintain your customizations.

Regards,

National Instruments

To the pessimist, the glass is half empty; to the optimist, the glass is half full; to the engineer, the glass

01-04-2018 07:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your responses.

I am familiar with the CLIP generator and have already created CLIPs and used them in a project.

The last point from Spex is exactly what I am trying to do. This helps out a lot! Things are becoming more clear but I am still a little hazy on some specific details.

In that help step it says to search for the ImplementationList tag in the xml file. I have found that in my generated CLIP and I see 2 implementations: a .vhd and .xdc file that came from the CLIP generator. What file types am I allowed to reference here? One particular vendor I am looking at getting IP from said they provide an encrypted IP file. I am working on getting the details of this, but to better understand that capabilities of the SOM I would like to know what all can be imported? Also are there limitations to what this IP can contain? Are the limitations what is listed here and here? Maybe it is just a lack of my VHDL understanding since I am not very familiar with VHDL. Are there any examples that import IP that I can look at, or sample IP that I can test importing into the CLIP?

Thank you,

Brad

Certified LabVIEW Architect

01-05-2018 09:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

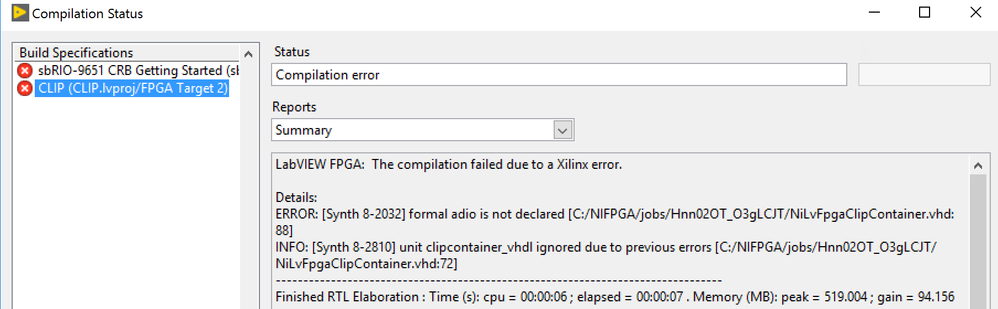

After digging around I did find an example in the LabVIEW examples and have been trying to integrate that into my 9651. I started with a completely blank clip (used clip generator and did not check anything to get a basic clip), and then tried adding the "DemoClipAdder" into the TestClip for my 9651. I got it down to 1 error

I can't figure out why it is complaining about adio. It only complained about it when I added the demoadder code.

I attached the project and clip files and hopefully someone can give me some insight into what I am doing wrong. I had to completely guess and do trial and error to piece the xml together so there could be something wrong about that.

Certified LabVIEW Architect

01-05-2018 02:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Brad,

I looked at your attached modifications and see some of your issues. It looks like you've left the TestClip VHDL untouched and only modified the TestClip XML. This will provide information about the DemoClipAdder signals to the LabVIEW project, but won't correctly implement the DemoClipAdder IP. You should modify the VHDL to include the DemoClipAdder logic. This could be done by implementing the DemoClipperAdder IP as a component in the TestClip top-level VHDL or by directly inserting the DemoClipAdder logic into TestClip.

Additionally, you should remove the DemoClipAdder entities from the <TopLevelEntityAndArchitecture> portion of the XML. The TestClip VHDL should remain your only top-level entity.

However, if you're not very familiar with VHDL and would prefer to avoid editing the socketed CLIP altogether there are other options. You could first generate a standard socketed clip to provide access to the DIO pins that you need. This would allow you to access those pins via an IO node on your FPGA VI. From there you would implement your third-party IP in the VI either through User-Defined CLIP or IP Integration Node. This method is a little more roundabout but would allow you to import the third-party IP without custom changes to the VHDL. If there's no specific reason why you need the third-party IP included in the socketed CLIP then this might be worth looking into.

Will

National Instruments

01-08-2018 09:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Will. This looks like exactly what I am looking for.

Your second option where I would implement my third party IP through a User-defined clip or IP Integration Node would probably not work for my end goal. I need something that allows the 3rd party IP to access the FPGA IO.

I have successfully compiled and run code integrating the 3rd party IP as a component in the top level vhd file.

I have a question still. Is there documentation on what the xml schema is? Particularly what all the different names are and mean (SignalList, Singnal, TopLevelEntityAndAchitecture)?

Just to document the process for adding in 3rd party IP and to verify I have things right. The process would be:

1. Start from Top Level clip

2. Modify .xml

a. add in ImplementationList of 3rd party vhd file path

b. add to SignalList Signals for the correct Interface for the IO / variables

3. modify top level .vhd file

a. add 3rd party vhd file as a component to the top level vhd file

i. 3 things needed to be done.

1. add component I/O in the port of the top level entity

2. add component definition

3. add instantiation of component in the architecture (after begin) of top level vhd

A helpful website I used was this and this.

My next step is to try to incorporate something that actually uses the FPGA I/O pins. Hopefully the process is the same.

Attached is modified files from above. Basically removed democlipadder from TopLevelEntityAndAchitecture, and modified TestClip.vhd to include the democlipadder as a component. I am posting these in case someone else is trying to do the same thing as I am.

Brad

Certified LabVIEW Architect

01-08-2018 11:09 AM - edited 01-08-2018 11:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Brad,

You can find documentation for all those XML tags here:

LabVIEW FPGA 2017 Help: Defining the IP Interface

The process you list is valid, however I do want to point out one additional thing. In order to access the IO you'll need to modify the top-level VHDL to assign the aDio_in, aDio_out, and aDio_enable signals to the appropriate pins of your third-party IP. It's these aDio signals that ultimately route to the IO. You'll notice that if you add a DIO line in the CLIP generator, VHDL is created to assign the in, out, and enable pins to the appropriate aDio signals. You may have already accounted for this, however it looks like your files didn't get attached so I wasn't sure.

Will

National Instruments

01-08-2018 11:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Will,

I have not accounted for that. Thank you for pointing that out, it will save me some trouble!

I re-attached the files here since they were missed before.

Certified LabVIEW Architect

07-12-2021 08:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, this link is broken, can you tell me how to solve this problem?