- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sbRIO-9609 not able to compile CAN & FPGA RMC IO in the same VI?

Solved!04-06-2021 09:32 AM - edited 04-06-2021 09:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

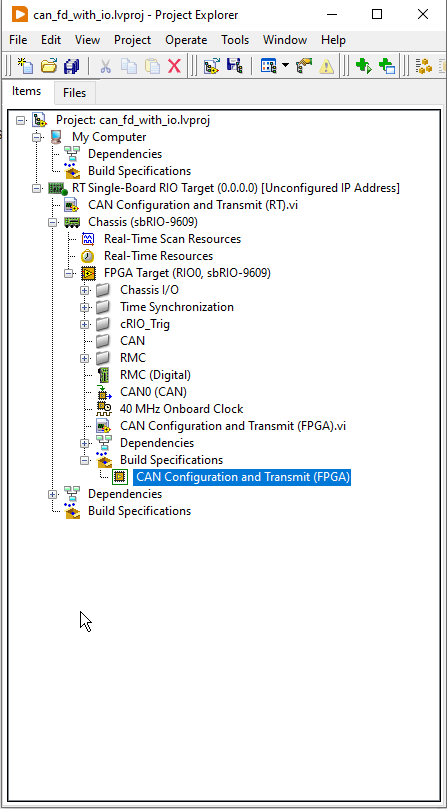

I am currently trying to utilize the CAN Port and the GPIOs on the RMC connector of a sbRIO-9609 at the same time, without any success yet. To illustrate my issue I have used the sbRIO CAN Programmatic Configuration.lvproj (examples\CompactRIO\Chassis Specific\sbRIO Onboard CAN Communication\sbRIO Onboard CAN Programmatic Configuration) example from the Example Finder and extended it by adding a Read I/O node for RMC Pins in a second loop.

When I try to build the VI with only the CAN Implementation it works, the moment I add the RMC I/Os it fails.

Any suggestions or ideas what is going wrong here?

I am using LabVIEW 2020 SP1 (32 Bit) + Vivado 2019.1 + RIO-Driver 20.5

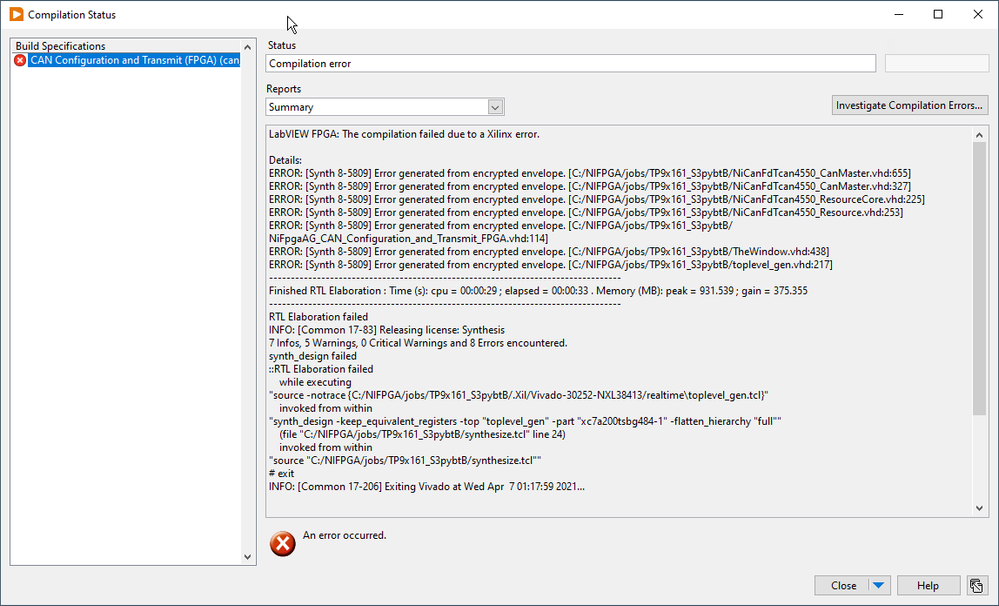

The error log shows issues with the Tcan4550*.vhd implementation:

WARNING: Default location for XILINX_VIVADO_HLS not found:

WARNING: [Common 17-306] Update version (2019.1.1_AR73110) does not match product version (2019.1.1).

****** Vivado v2019.1.1_AR73110 (64-bit)

**** SW Build 2580384 on Sat Jun 29 08:12:21 MDT 2019

**** IP Build 2579722 on Sat Jun 29 11:35:40 MDT 2019

** Copyright 1986-2019 Xilinx, Inc. All Rights Reserved.

# package require struct::list

# package require struct::set

# set_param synth.elaboration.rodinMoreOptions "rt::set_parameter max_loop_limit 1000000;"

# read_vhdl [glob *.\[vV\]\[hH\]\[dD\]]

# set_property top "toplevel_gen" [current_fileset]

# auto_detect_xpm

auto_detect_xpm: Time (s): cpu = 00:00:01 ; elapsed = 00:00:08 . Memory (MB): peak = 298.273 ; gain = 0.000

# if {[llength [glob -nocomplain *.\[xX\]\[dD\]\[cC\]]] > 0} {

# set CoreXDCFilesFH [open CoreXDCList.txt r]

# set xdc_files_xci [split [read $CoreXDCFilesFH] "\n"]

# close $CoreXDCFilesFH

# set xdc_files_all [glob *.\[xX\]\[dD\]\[cC\]]

# set xdc_files_source [::struct::set difference $xdc_files_all $xdc_files_xci]

# set xdc_files [read_xdc $xdc_files_source]

# foreach xdc_file $xdc_files_xci {

# if {[file exists $xdc_file]} {

# lappend xdc_files [read_xdc -ref [file rootname $xdc_file] $xdc_file]

# }

# }

# set_property PROCESSING_ORDER {LATE} [get_files $xdc_files]

# }

# read_edif [glob *.\[eE\]\[dD\]\[fFnN\]]

# set_msg_config -id "Synth 8-3431" -suppress

# synth_design -keep_equivalent_registers -top "toplevel_gen" -part "xc7a200tsbg484-1" -flatten_hierarchy "full"

Command: synth_design -keep_equivalent_registers -top toplevel_gen -part xc7a200tsbg484-1 -flatten_hierarchy full

Starting synth_design

Attempting to get a license for feature 'Synthesis' and/or device 'xc7a200t'

INFO: [Common 17-349] Got license for feature 'Synthesis' and/or device 'xc7a200t'

INFO: [Device 21-403] Loading part xc7a200tsbg484-1

INFO: Launching helper process for spawning children vivado processes

INFO: Helper process launched with PID 28936

---------------------------------------------------------------------------------

Starting RTL Elaboration : Time (s): cpu = 00:00:10 ; elapsed = 00:00:11 . Memory (MB): peak = 733.934 ; gain = 178.105

---------------------------------------------------------------------------------

WARNING: [Synth 8-5858] RAM sInputRx_reg from Abstract Data Type (record/struct) for this pattern/configuration is not supported. This will most likely be implemented in registers

WARNING: [Synth 8-5858] RAM dShifter_reg from Abstract Data Type (record/struct) for this pattern/configuration is not supported. This will most likely be implemented in registers

WARNING: [Synth 8-5858] RAM bSelectedInputDataToDmaArray_reg from Abstract Data Type (record/struct) for this pattern/configuration is not supported. This will most likely be implemented in registers

WARNING: [Synth 8-5858] RAM bNiDmaInputDataToDmaShiftReg_reg from Abstract Data Type (record/struct) for this pattern/configuration is not supported. This will most likely be implemented in registers

WARNING: [Synth 8-5858] RAM cDataShiftReg_reg from Abstract Data Type (record/struct) for this pattern/configuration is not supported. This will most likely be implemented in registers

INFO: [Synth 8-6157] synthesizing module 'FDCE' [C:/NIFPGA/programs/Vivado2019_1/scripts/rt/data/unisim_comp.v:13448]

INFO: [Synth 8-6155] done synthesizing module 'FDCE' (101#1) [C:/NIFPGA/programs/Vivado2019_1/scripts/rt/data/unisim_comp.v:13448]

INFO: [Synth 8-6157] synthesizing module 'FDCE__parameterized1' [C:/NIFPGA/programs/Vivado2019_1/scripts/rt/data/unisim_comp.v:13448]

INFO: [Synth 8-6155] done synthesizing module 'FDCE__parameterized1' (231#1) [C:/NIFPGA/programs/Vivado2019_1/scripts/rt/data/unisim_comp.v:13448]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/NiCanFdTcan4550_CanMaster.vhd:655]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/NiCanFdTcan4550_CanMaster.vhd:327]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/NiCanFdTcan4550_ResourceCore.vhd:225]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/NiCanFdTcan4550_Resource.vhd:253]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/NiFpgaAG_CAN_Configuration_and_Transmit_FPGA.vhd:114]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/TheWindow.vhd:438]

ERROR: [Synth 8-5809] Error generated from encrypted envelope. [C:/NIFPGA/jobs/K0Tmhi5_s2813ze/toplevel_gen.vhd:217]

---------------------------------------------------------------------------------

Finished RTL Elaboration : Time (s): cpu = 00:00:25 ; elapsed = 00:00:27 . Memory (MB): peak = 933.199 ; gain = 377.371

---------------------------------------------------------------------------------

RTL Elaboration failed

INFO: [Common 17-83] Releasing license: Synthesis

7 Infos, 5 Warnings, 0 Critical Warnings and 8 Errors encountered.

synth_design failed

::RTL Elaboration failed

while executing

"source -notrace {C:/NIFPGA/jobs/K0Tmhi5_s2813ze/.Xil/Vivado-27424-NXL38413/realtime\toplevel_gen.tcl}"

invoked from within

"synth_design -keep_equivalent_registers -top "toplevel_gen" -part "xc7a200tsbg484-1" -flatten_hierarchy "full""

(file "C:/NIFPGA/jobs/K0Tmhi5_s2813ze/synthesize.tcl" line 24)

invoked from within

"source "C:/NIFPGA/jobs/K0Tmhi5_s2813ze/synthesize.tcl""

# exit

INFO: [Common 17-206] Exiting Vivado at Fri Apr 2 12:59:48 2021...

Solved! Go to Solution.

04-06-2021 05:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi wromeo,

We've got a known issue with mixing CAN and RMC I/O in the same FPGA bitfile right now. The compiler is picky about what order the resources are compiled in. Luckily, there's a way you can force the compilation order to work properly.

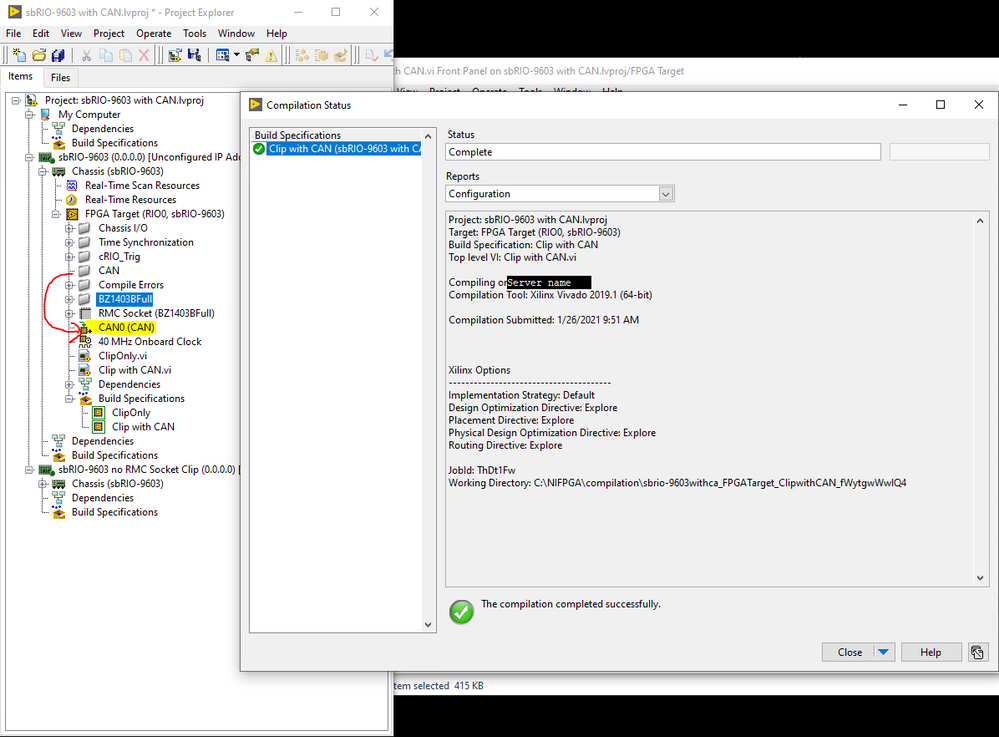

In your .lvproj file, you'll want to drag the CAN item underneath the RMC Socket item, as shown in the image below:

Product Support Engineer - sbRIO

National Instruments

04-06-2021 06:20 PM - edited 04-06-2021 07:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi NickelsAndDimes,

just some trials later playing with the xlinx options and regenerating the intermediate files finally did work. Nevertheless, when is it planned to fix this problem?

thanks for your response, I tried now several times (screenshot below). Changing the order does not do much to my problem. Furthermore your screenshot shows sbRIO-9603, I am using a sbRIO-9609. Also your LabVIEW version is prior to LabVIEW 2020 SP1. Also notice that the CAN driver for the sbRIO-9609 was not available in prior LabVIEW versions (especially not in LabVIEW 2019).

04-06-2021 06:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi wromeo,

Like I said, there's a known issue. I have not yet attempted to reproduce your issue because it matches the known behavior. This behavior is consistent across multiple sbRIO devices with the same architecture, including both 9603 and 9609. I just happened to have that screenshot handy from the last time I helped someone with this issue.

Also, the job title in my signature is misleading, it is not my job to respond to posts on this forum. I am responding because I want to help you, not because I have to. Being snarky about the quality of my assistance doesn't make me more excited to help you.

I see you're using the 9694 digital breakout RMC board. I was under the impression that you were using a custom RMC with a CLIP that you had generated yourself, and a CAN port in that CLIP. I suspect that it's related to the same root cause, but the details might be slightly different with the digital RMC. I'll need to talk to a couple of people on the driver side to get their thoughts.

Product Support Engineer - sbRIO

National Instruments

04-06-2021 06:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Glad to hear you got it working.

Product Support Engineer - sbRIO

National Instruments

04-06-2021 06:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks!

04-18-2022 12:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This trick of moving the CAN0 resource under the RMC Socket doesn't work. I tried opening up the Example LVproj sbRIO CAN Programmatic Configuration. It has a sbRIO 9609 as well and it gives the same error in both locations.

08-08-2022 05:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

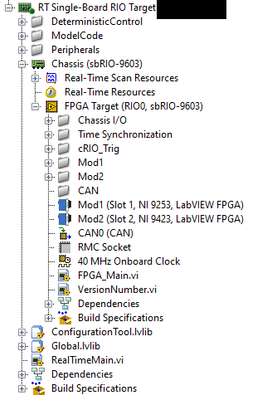

I was having these same issues and errors. Turns out I had to move the c series modules above the CAN port as shown below