- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA/FlexRIO Error -61046

Solved!08-04-2016 03:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

Please, for the love of god can somebody take a look at the attached FPGA project I knocked up and tell my why it is that every time I run, as soon as it tries to read/write on the Host does it return error -61046? A screen shot of the error is included in the attached .zip file.

I've made many FPGA programmes before with no issues, all using the same FPGA and FlexRIO module and never had this problem. If I run an example program it works fine so I'm confident the error lies in my programming, I just can see where!

As you can see all the clocks are internal and appear to be setup correctly as per the example programmes and the other FPGA programmes I've made before thus I'm stumped. Hopefully it's just my stupidity and lack of coffee.

Cheers in advance.

Mitch

Solved! Go to Solution.

08-15-2016 12:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The -61046 error usually occurs when you are trying to communicate with SCTL that uses a clock which is not running correctly. I would take a look at the clock you have connected to the SCTL and confirm that it is running as you expect it is.

08-22-2016 05:31 AM - edited 08-22-2016 05:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David,

Apologies for the late response but I've been away on holiday so only just seen your reply.

Before I went on holiday I pinged a service request to NI to see if they could resolve the issue as nobody had replied at that point. Here's their response:

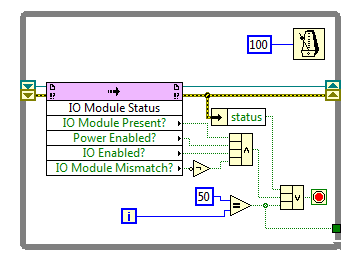

"I believe the issue you are seeing is that the FlexRIO Adapter Module and associated CLIP code, and therefore the AO Clock (IO Module Clock 1), are not ready by the time you start reading the indicators that are in Single Cycle Timed Loops that are clocked by the AO Clock.

Since that Single Cycle Timed Loop isn't being clocked the logic is no longer executing and the register (indicator) that you are reading from on the host isn't being updated. However, the host code doesn't know this and tries to read from that indicator still. When it tries to read from the indicator that isn't being updated, you get a timeout in the form of the error you are seeing."

They sent me a screen shot of some code to try which they believe will resolve the issue:

Once I get a chance I'll try the code and report back.

Cheers

Mitch

08-22-2016 05:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On a bit of a side note, I also asked why it is that all the examples run the separate AI and AO SCTLs from the same clock, even though in the manual it clearly states that the AI signals and AO signals must be accessed from within their respective clock domains, IO Module Clock 0 (AI) and IO Module Clock 1 (AO).

NI said that because the AI channels and AO are simultaneously sampled, if the ADC and DAC are being run off the same clock in System-Synchronous mode then all the channels should be synchronised.

I still need this clarifying somewhat because although running in this way definitely works (running the AI and AO SCTLs in my code off the same clock makes my issue disappears) and is beneficial as its all synchronised, I’m unclear as to what it means when it states they must be accessed from within their respective clock domain.

To me it reads as though some kind of violation is being performed if the AO is clocked by the AI but I’m guessing my interpretation of what it means is incorrect.

08-22-2016 01:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The FlexRIO driver ships two CLIPs for the 5781. A 'NI 5781" CLIP and a 'NI 5781 System Sychronous' CLIP.

The 'NI 5781' is what originally shipped with the FAM and is still shipped with the driver for legacy purposes. I would discourage the use of this CLIP since it utilizes regional clocks for IO Module Clock 0/1 which limit the amount of fabric that can be driven by those clocks to the fabric available in the respective region of the FPGA. The advantage of this CLIP is that the ADC and DAC can be clocked at different rates via a clock divider that the CLIP exposes.

The 'NI 5781 System Sychronous' CLIP is what is recommended for all new designs. It uses a global clock that which can target fabric in every region of the FPGA. This CLIP uses the same clock to drive both the ADC and DAC (IO Module Clock 0). IO Module Clock 1 is unused in this CLIP.

If you used the system sychronous CLIP and still had some logic driven by IO Module Clock 1 that would explain why you were getting the no-reponse error since IO Module Clock 1 is left unconnected in the system sychornous CLIP.

08-23-2016 02:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Morning David,

That explanation was perfect and fully explains why I'm seeing the error as well as why all the examples work plus my code when I make all the SCTLs run off Module Clock 0 (AI).

Knowing this important piece of information is clearly critical so it does beg the question as to why the project does not complain if you setup Module Clock 1 on the FPGA but then choose the System-Synchronous CLIP in the FAM properties (or vise-versa). The selection of the CLIP and Clock for any FPGA+FAM combination are inherently linked now knowing this.

If its definitely impossible to use Module Clock 1 when running System-Synchronous CLIP (i.e. there is no special mode where it can be utilised) then to me the project should know there is a guaranteed run-time failure and should not allow the project to be built nor run. It should also disable+grey out the Module Clock 1 option and give and explanation as to why like it does for other clock selections.

Cheers for your help David, much appreciated.