- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Allow Rotate 1D Array in SCTL with constant n

10-12-2016 07:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If n is constant, it should be a wiring operation and it shouldn't require multiple itterations so it should be allowed in a SCTL.

10-12-2016 07:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I just noticed I posted this in the wrong forum. Mods, can you move this to FPGA?

10-13-2016 09:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Use the Option link next to your message and Report to Moderator to request that it be moved.

I'd also suggest that you add some more detail to your post. Perhaps even an image as to what you are talking about. It would go a long way in clarifying what you are talking about and in selling your idea to entice people to kudo it.

10-13-2016 12:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

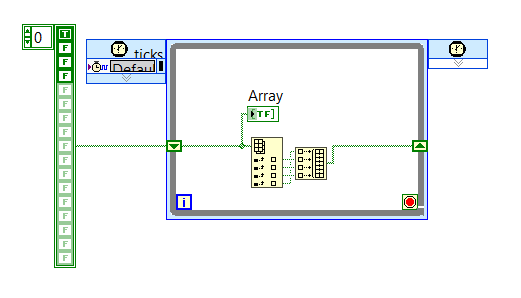

That's good feedback RavensFan. To clarify, currently, if you use rotate 1D array in a single cycle timed loop, you get an error like this:

I don't think there's any fundamental reason why that shouldn't be allowed. It was probably disallowed incase someone wired a control into the n terminal at the top.

10-13-2016 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It is probably because rotating an array is computationally expensive, and might not be guarenteed to execute in the given time.

Certified LabVIEW Developer.

10-13-2016 03:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Mythilt, in an FPGA (which is what this idea is actually for) a rotate with a constant for the number of elements to rotate should be nothing more than a routing issue. No computations needed. Admittedly, it probably is because of the non-constant rotations that it is not allowed inside of a SCTL.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

10-13-2016 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It should be equivalent to something like this which is a pure wiring operation and is allowed

10-14-2016 07:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Interesting, I did not know that FPGAs handled arrays that much differently. Have to do some reading on that. Makes sense due to the limitations of their embedded nature.

Certified LabVIEW Developer.