- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Analyzing 3 phase power quality

09-03-2015 10:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I recently started using labview for my master's thesis and this is the first time I'm posting on ni forum.

I'm working on a lab view project for analyzing 3 phase power quality and I'm using sbRIO 9606 + NI 9683.

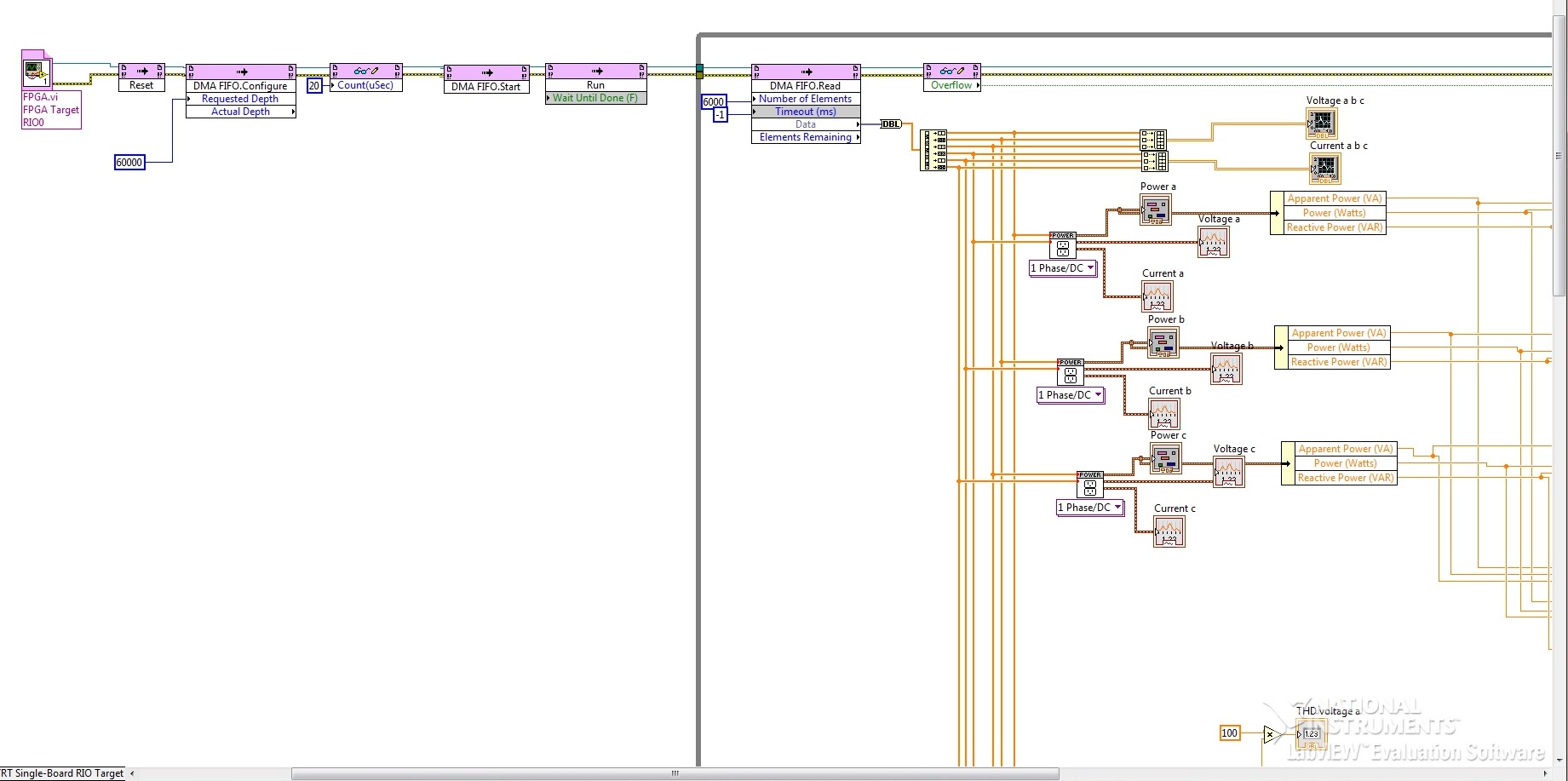

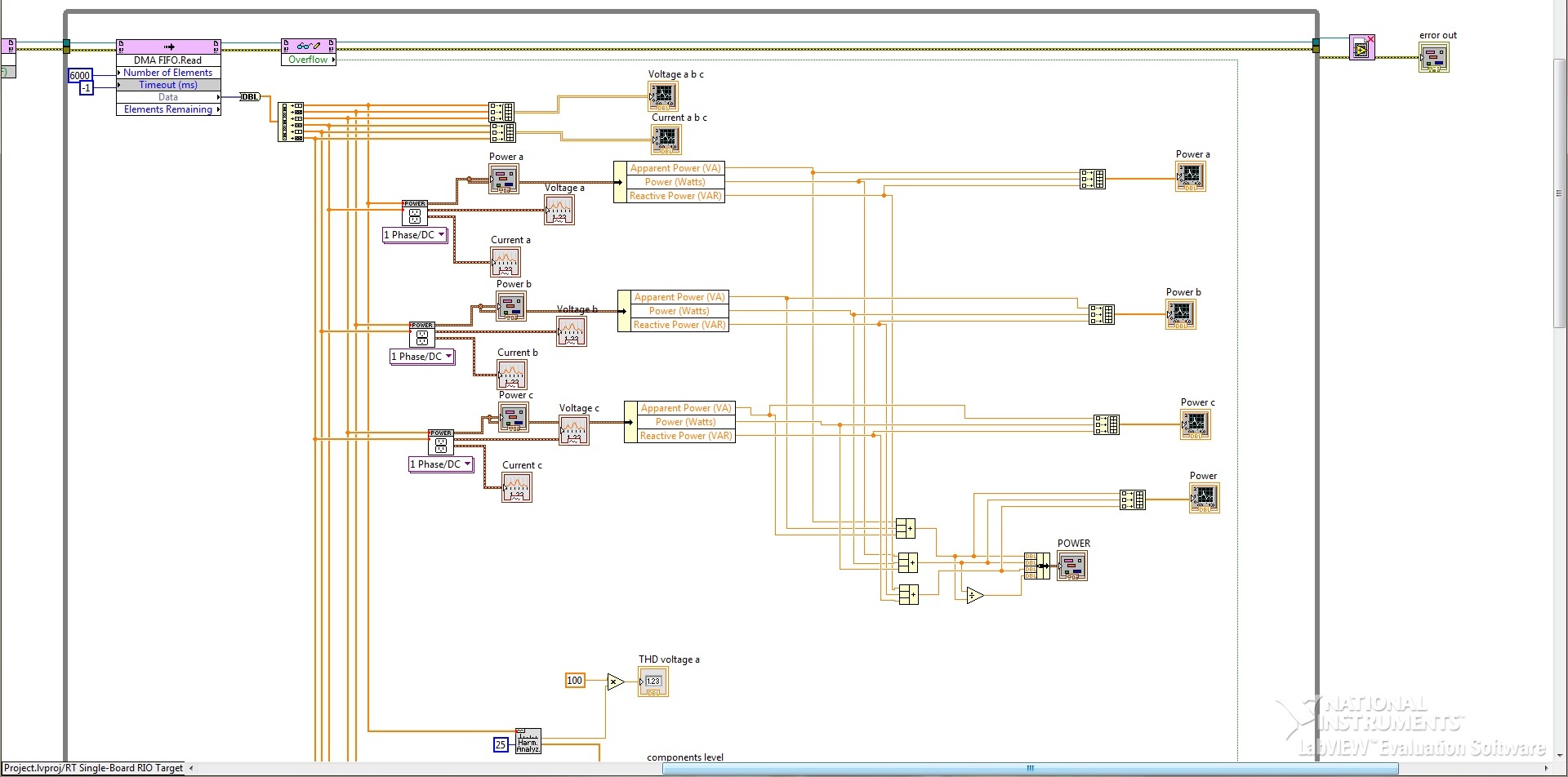

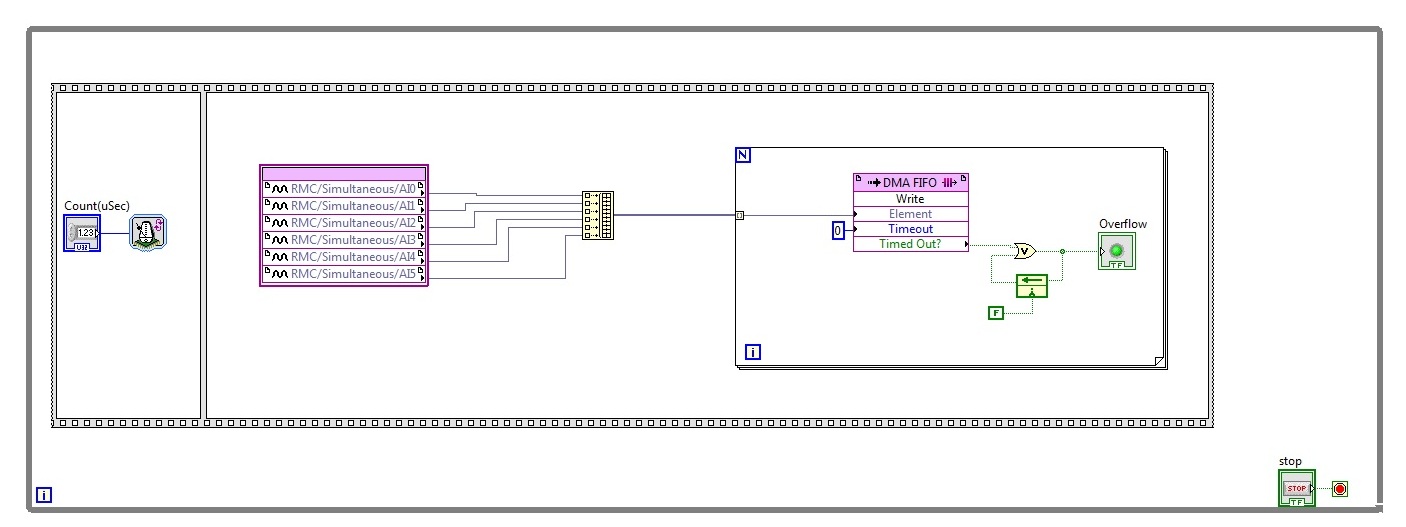

I've made a fpga.vi that acquires data from 6 analog inputs (3 phase system currents and voltages) and that transfers data to the host using DMA fifo channel. Here's the picture of fpga.vi.

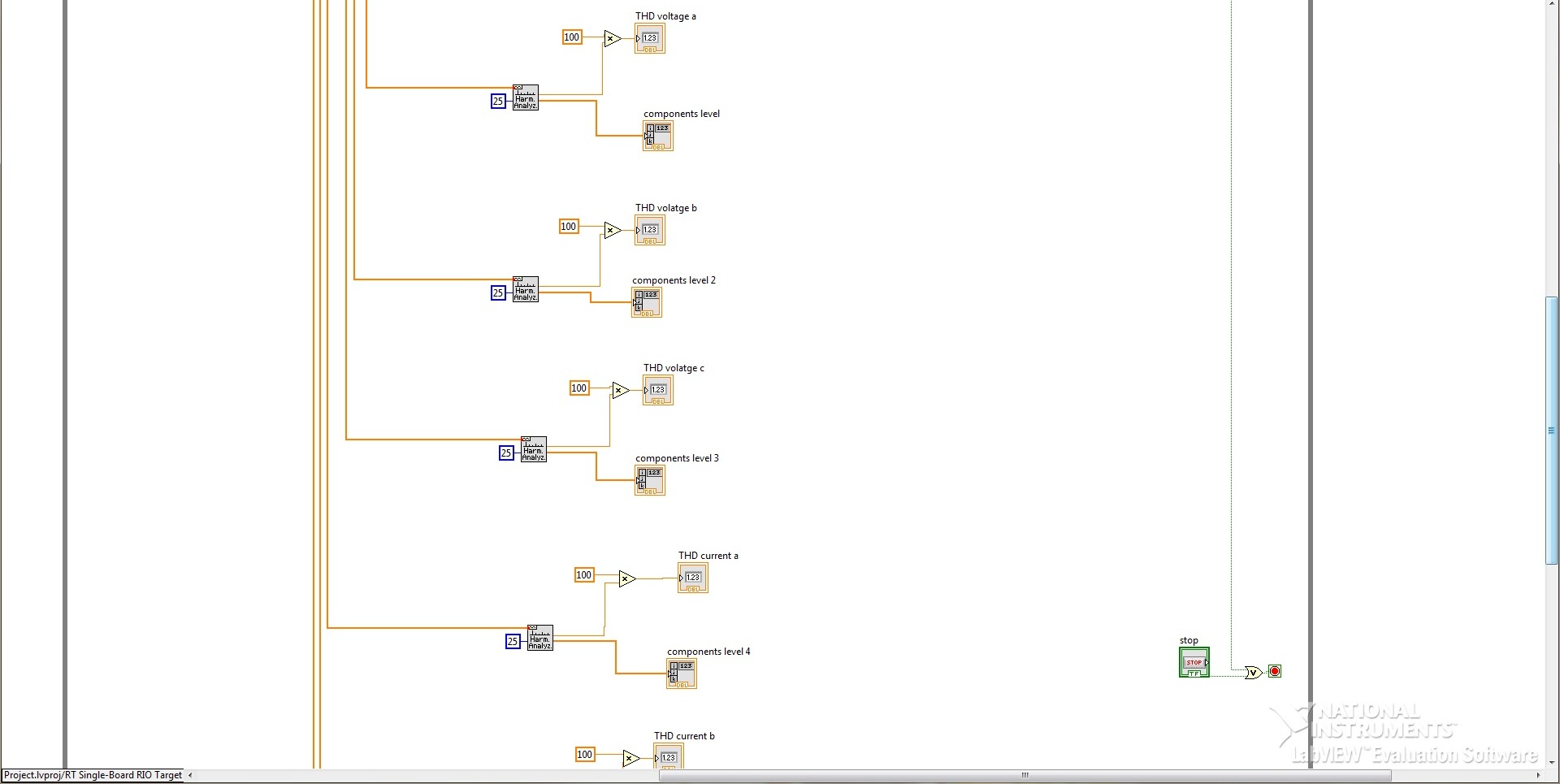

The problem that I'm having is that overflow occurs. I've read that the size of the buffer needs to be 5 times bigger than the number of elements that I'm reading. So, when I chose the sampling rate to be 50kHz and when I was reading 6000 elements from buffer ( 6000 elements divided into 6 arrays means that I have 1000 elements per channel with the sampling period of 20 microsec. giving 20 ms for one input; I did this so that I have at least one period of fundamental frequency for analyzes) and left out the part of the vi that calculates harmonics I didn't have an overflow. But when I try to execute the whole host.vi, overflow appears even when I lower my sampling frequency to 20kHz. How can I do the whole analyzes without the overflow?

If needed, I've attached my lab view project.

Thanks in advance.

09-03-2015 04:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I do not have the FPGA or Electrical Power Suite so I cannot look at all your code.

I suggest you switch to a Producer/Consumer architecture for your Host.vi. Put the DMA FIFO Read in the Producer. Put all the analysis VIs in the Consumer. If the analysis still cannot keep up, try reducing the number of times you update indicators, especially graphs, on the front panel. Your users cannot perceive, interpret and understand 50 updates per second. The eye-brain system does not work that fast.

Lynn

09-05-2015 07:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Cuold you please explain the use of producer/consumer architecture? I also have trouble understanding which part of my host.vi is executed on microcontroller and which on my PC.

09-06-2015 11:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The Producer/Consumer architecture uses two parallel loops to separate the production of data (read from DMA FIFO) from the consumption of the data (analysis, display, save to files, ...). The reason for this is to allow the processes to occur at different rates. You are reading the data at 50 Hz. However, the human eye-brain combination cannot acquire and process data that fast so it makes no sense to update the graphs or numeric indicators more than 5-10 times per second. All recent versions of LV come with a template or example of Producer/Consumer to help you get started.

In effect your FPGA/host is already a sort of producer/consumer architetcture. From your description of the problems you are having with buffer overflow it seems that having everything on one loop on the host side is too slow to keep up with the acquisition.

Typically data is transferred between the loops via a queue. The queue can serve as a buffer, the size of which is limited by the amount of memory available in the host computer. Arrays of data must be in contiguous memory locationsand other factors may limit the maximum amount of dat which can be buffered but it should still be much larger than the FIFO buffer.

Decide how much of the data needs to be analyzed and displayed. If 5 display updates per second is adequate, only analyze that much. If you need to analyze all the data but only display a subset, consider streaming the data to a file for later analysis.

The Harmonic Distortion Analyzer.vi comes in a version which accepts an array of waveforms as inputs. I have not tested but that my be faster than having 6 separate copies of the single waveform input version. You may also be able to speed it up by making a copy with a different name and removing code for things which you are not using.

Lynn

09-08-2015 03:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've been going through some discussions and examples of consumer/producer loops and, as I unerstand it, I have to read more data at once in consumer loop than I write in producer loop because consumer loop is slower. Am I correct?

Also I'm reading 6000 elements from DMA fifo buffer so does rt buffer have to be defined for arrays of 6000 element as well? And if so, if I want to read more than I write, do I have to put rt buffer read in a for loop?

09-08-2015 09:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I do not have any experience with RT so I cannot help with that part.

The loop which reads the data from the DMA FIFO buffer needs to run fast enough that the buffer never overflows. After reading that on the host side, immediately stuff the data into another, much larger buffer. Then read the next chunk. The consumer loop then reads data from that larger buffer at sizes and rates whihc will keep it form overflowing.

Lynn

11-13-2016 06:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Holle,Kovac,recently,I am writting a code for calculating the active power,but there has been no success.Can you share me with the EPM_Power.vi in the code you have showed?I would be grateful.