- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CompactRIO Digital lines max speed

02-21-2023 03:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am planning to buy a CRIO and use LabVIEW which I would like to use to sample 6 DIO lines with sampling rate 100 MHz, and when finding a negative edge in a specific DIO line (which is 10 MHz clk) I will save the data in a FIFO which I will read after saving data of 10 seconds (100 MB data).

I have several questions:

1- I can't find a C-Series digital input or multifunction I/O modules that can support sampling rate (100 MHz), is there any module that can support this, or the DIO lines will only be limited with the speed of the FPGA in this case as I am not using the scan mode.

2- Is there a CRIO model that has a FIFO or non-volatile memory that can handle 100 MB data size

3- I am planning to process this data afterwards, I have two options to do this, the first is using the FPGA, if so what is the best solution to copy this big sized data between parallel loops in LabVIEW FPGA, the second option is to process this data using the CRIO real-time processor, in this case what is the best option to copy the data from FPGA to processor without any data loss (I am thinking to use FIFO if the size is enough)

4- Can I connect a monitor directly to the CRIO and consider it as a standalone test setup or I will need to have a PC/Laptop in case I need to have a user interface (front panel)?

Please suggest if you have any other idea rather than the CRIO to use for this application.

02-21-2023 03:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would look at PXIe cards as well. I think cRIO may not be able to support what you are looking for.

See chapter 6 of the compactRIO developer's guide for information on interfacing between the c-series module and the FPGA.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-21-2023 03:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

cRIO cannot do that fast. The cRIO FPGA has a 40MHz clock and the fastest c-series module is also in that range (9402). You may have to go with a FlexRIO or simply a HS DIO card (PXIe).

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

02-22-2023 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok, Can I have an external clock to the CRIO to be used for sampling the data instead of the internal clocks so that I may not need in this case to use 100 MHz to sample the 10 MHz external clock and instead of that use this clock as the main clock of my system.

02-22-2023 12:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, is it required to make the system stand-alone? Or, is system footprint required to be as small as possible?

If the system is not required to be stand-alone, and all you need is digital input / output, PXIe-1090 + PXIe-7820 may be a good fit for you.

Total cost is about 6,000 USD for the set of two, and a host PC with Thunderbolt3 IF is needed.

Digital Input of PXIe-7820 can work up to 80MHz and does not reach up to 100MHz, if it is still fast enough for you to do oversampling for negative edge of your 10MHz clock, you may go with internal 80MHz clock.

Also, PXIe-7820 can take external clocks, so, if 80MHz is not fast enough, yyour 10MHz clock may be imported to PXIe-7820 as an external clock.

PXIe-1090 is a wonderful option for a low-cost and small footprint application, if using a laptop is allowed. I provided a system with PXIe-5785 + PXIe-1090 for my customers, using 2x2 3.2GSps IOs.

One caveat for using PXIe-1090 is its per-slot bandwidth is 985MB/sec, but it is x1 Gen3 link. Therefore, if your module is x1 Gen2 link for example, per slot can handle only 500MB/sec of data. I guess 500MB/sec may be enough for your case.

As for data processing, 100MHz clock is not so fast and you can do data processing in the same clock domain of IOs. If you think of doing signal processing on host-side, DMA FIFO is the only way for the case to transfer data, as it is explained in FPGA training course.

02-22-2023 01:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I forgot to mention about terminal block and cable required for 7820.

also, I remembered that I once used external clock with sbRIO-9651. Some other sbRIO products can handle external clock as mentioned in the thread below.

https://forums.ni.com/t5/LabVIEW/assign-a-Ext-clock-to-SbRIO-Clip/td-p/3599378

I wonder if NI keeps providing cRIO/sbRIO product lines, because they squeeze their focus into PXI-based solutions and cRIO based solutions such as InsightCM were off-loaded to NI partners. Also, DCAF project was ended. cRIO/sbRIO/IC could have much better changed the engineering and scientist life at least last ten years, if LabVIEW / RT / FPGA had been provided for better cost and with better training materials. In my opinion, NI has closed the possibility of their wonderful products by themselves.

anyways. I love NI products.

02-22-2023 02:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Also, because I don't think it was mentioned earlier in this thread, digital I/O can't run at arbitrary speeds on a cRIO so you might not even be able to even compile an FPGA VI with digital I/O nodes in a 100MHz timed loop.

02-23-2023 01:03 AM - edited 02-23-2023 01:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As Jacobson mentions above, cRIO digital IO nodes cannot be placed inside SCTL, while it can be for digital IOs on PXIe-78xx and RMC DIO with sbRIOs.

I a bit further dag into sbRIO specifications. As mentioned below, digital input may work up to 60MHz, and they can be placed inside SCTL.

What is the Maximum Speed of the DIO on the RIO Mezzanine Card?

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000fys0SAA&l=en-US

Also, external clock can be imported by using CLIP generator for sbRIO.

Error of external clock for CLIP (with sbRIO 9651)

https://forums.ni.com/t5/LabVIEW/Error-of-external-clock-for-CLIP-with-sbRIO-9651/td-p/3907922

I could not find a spec for maximum data transfer rate from RT to FPGA for sbRIO-9609. If you transfer 6 lines of digital input at 100MHz SCTL to do post processing on RT, pad upper 2bit so that you get U8 data for transfer. Packer can be implemented if the upper 2bit is desired not to be wasted.

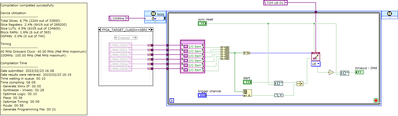

Below is a very simple test VI and I do not have sbRIOs with me right now, but compilation ended successfully.

sbRIO may not be sold for a single unit, though, Iguess. Also, it may be required to develop a casing for sbRIO, because it is a PCB.

02-23-2023 05:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@UMASO wrote:

As Jacobson mentions above, cRIO digital IO nodes cannot be placed inside SCTL,

I currently have the DIO nodes for a 9402 on a cRIO-9040 inside of a SCTL. I am getting the 25ns resolution (40MHz). For my application, this is just barely fast enough.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

02-23-2023 08:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for correcting my post above. Crrect statement should be "cRIO DIO can be placed inside SCTL with 40MHz onboard clock, and cannot be placed any other clocks such as derived clocks."

By the way, in your configuration with 9402, DI is working at 40MHz, while its specification is 16MHz with 4-channel, and 20MHz with 2-channel, as described in 9402 specification below.

Maximum I/O switching frequency

https://www.ni.com/docs/en-US/bundle/ni-9402-specs/page/specifications.html

How many channels are you using with the current configuration? 4 channels?