- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA: Cloud Compile Service compiles take very long

03-24-2016 04:44 AM - edited 03-24-2016 04:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've started using the Cloud Compile Service to compile our FPGA code.

I was a bit surprised by the differences compared to the local compile server.

I'm using LabVIEW 2012 SP1 with the Xilinx Tools 13.4 (7965R card).

When compiling on my local Windows 7 machine our FPGA code takes around 2.5 hours to compile. On the Cloud Compile Service the same VI takes around 4 hours (several compilations on different days). I thought the compile machines are dedicated (Linux?) machines so I was expecting compilation times to be faster than on my standard Windows 7 machine.

With a small test VI the difference is even much bigger: it compiles in 7 minutes on my local machine, but takes 45 minutes on the Cloud Compile Service.

What I observed is that the LUT utilization is around 10% smaller (!) when compiling on the Cloud Compile Service. Does this indicate it uses different optimization flags for the compiler? I remember that for the old Virtex-II target I could specify some compiler optimizations (area, speed, balanced or similar), but for the Virtex-5 I don't have any options.

Any insights?

03-24-2016 08:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What's your local machine? This is useful to consider when comparing the two times. On my machine, the times are similar enough I see the difference as neegligible. But, my machine isn't anything special.

03-24-2016 08:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My machine isn't anything special, either. It's already 4 years old, an Intel i7-2600 CPU (3.4 GHz) running Windows 7. I have 16 GB of RAM (mainly to run Virtual machines).

I configured the Compile Worker to run on a single core (according to the great tip here: http://forums.ni.com/t5/LabVIEW-FPGA-Idea-Exchange/Multi-core-Compiling/idc-p/2301338#M297), which reduced the compilation times by about 40%.

03-24-2016 09:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So I imagine that when you send a job to the compile server, it gets queued up - so you might have to wait until your compilation hits the front of the queue. I also doubt they've implemented the single core change to speed up the compilations. I think the both of those combined probably explains the increased compile time.

03-24-2016 09:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If it needs to wait that is indicated as waiting in queue. I'm comparing the actual compile times, this does not include the wait times.

And as far as optimizations go, I would expect for dedicated compile machines to have all possible optimizations applied.

And even if they didn't, it can't explain the 45 minutes vs. 7 minutes compile time for a simple VI.

Maybe the machine is running several compilations in parallel (on virtual machines?) so they fight for CPU time.

Again, device utilization (LUTs) is also different, so that suggests the cloud compile machines use some compiler flags which I don't have access to.

04-01-2016 03:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I did some more compiles both locally and on the cloud compile service.

It looks to me like the cloud compile uses around 10% less LUTs compared to the local compile server, but the cloud compile seems to have more problems meeting the timing requirements.

Does the cloud compile try to optimize the design for area, but the local compile optimizes for speed? Any insight here?

How can I access these compiler flags in a local compilation?

04-01-2016 04:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

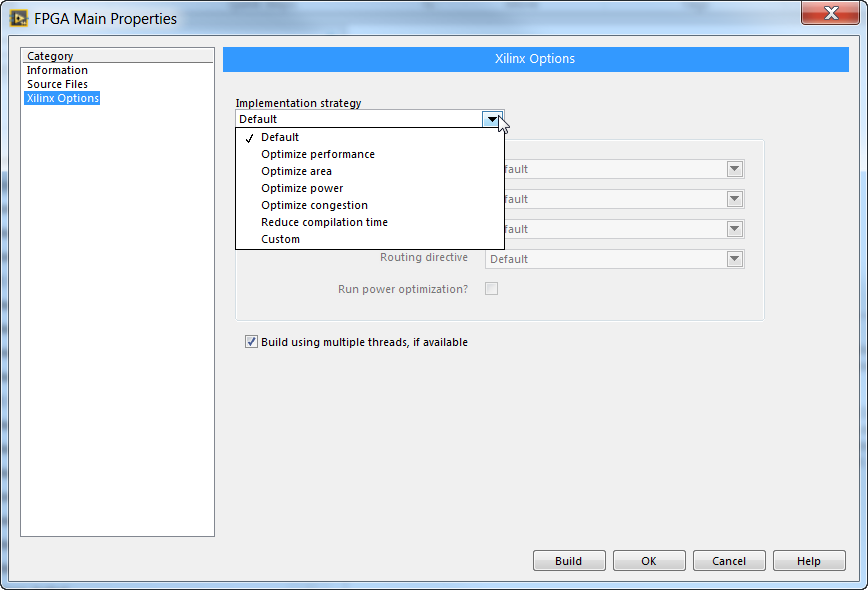

The only options I'm aware of are the ones that you can specify in the FPGA build specification:

04-01-2016 04:31 AM - edited 04-01-2016 04:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This is exactly what I meant, and I remember these settings were available for the Virtex-II, but I don't have these available for our Virtex-5 FlexRIO target (LV2012, Xilinx Tools 13.4). What target and LV version do you use?

I remember NI saying that for FlexRIO targets it is automatically set to optimize for speed (I guess this would be the "Optimize performance" setting).

04-01-2016 04:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

04-01-2016 04:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

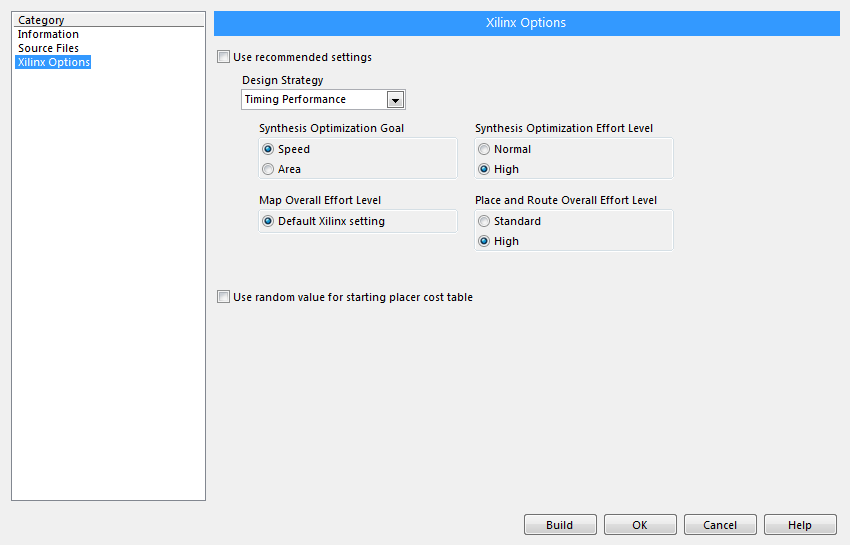

In LV2012 for the Virtex-II I have these options:

For the FlexRIO (7965R) there's no Xilinx options tab.