- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Write/Read DMA FIFO for multiple channels - FOR loop vs multiple FIFOs

11-27-2018 03:32 PM - edited 11-27-2018 03:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

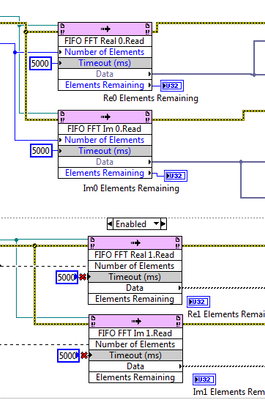

I'm using LabVIEW 2014 with FPGA module. Hardware is NI 9146. I have multiple Analog Input channels of which I need to write data to DMA FIFO in the FPGA VI, and then read from DMA FIFO in the host VI.

What is the "correct" method to write/read:

1. Build an array with the analog inputs, use FOR loop to Write, and use Decimate Array to segregate

2. Use multiple FIFO's to write and corresponding FIFO's to read.

I'm keeping track of elements remaining, to make sure there is no overflow.

I've tried both methods, and I get different end results. I'm not sure which method guarantees data integrity.

Can someone throw some light on this please?

Thanks.

11-28-2018 07:05 AM - edited 11-28-2018 07:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You have made tests, get different results and are not sure which one guarantees data integrity?

I think you need to think more about what you are doing so that you can immediately reject one or both approaches if the received data does not correspond to what you were expecting.

In other words, build a test where your starting point is known and then try to pass this via DMA and check to see if the end result is correct or not. What is "right" depends a lot on what exactly you are trying to do.

PS One thing I will say, if the data width of your individual dat apoints is 32 bits or less, place them both in a single 64-bit value and use a single 64-bit DMA instead of trying to synchronise 2 DMAs.

11-29-2018 09:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, what you said occurred to me right after I posted this question. So I'm in the process of testing with known signals.

But I still want to know if there is an "official" recommended method for multiple channels.

11-30-2018 12:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No official recommendation that I could find for your specific implementation. The closest we get is recommending DMA FIFOs for FPGA/Host data transfer.

Whichever route successfully reports your known input would be "recommended" in this case.

Technical Support Engineering

National Instruments

12-03-2018 04:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Kevin.MN wrote:

No official recommendation that I could find for your specific implementation. The closest we get is recommending DMA FIFOs for FPGA/Host data transfer.

Whichever route successfully reports your known input would be "recommended" in this case.

Thanks for your reply.

I also have a related question about the behavior of the 'FFT Express VI' on the FPGA side and the 'FFT-to-Spectrum' VI on the host side. Is there any difference in those functions between LV2014 and LV2016?

12-04-2018 11:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Looks like you've done the proper thing and moved the follow-up question to a new thread. I'll check in on the other thread, and ensure that it doesn't die.

Technical Support Engineering

National Instruments

12-04-2018 02:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Kevin.MN wrote:

Looks like you've done the proper thing and moved the follow-up question to a new thread. I'll check in on the other thread, and ensure that it doesn't die.

Ok Thanks.