- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Flatten floating point on FPGA for multichannel DMA

09-23-2013 01:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Flatten to boolean array (free on FPGA) and then re-cast to U64 (Again essentially free if the number of bits actually match). On the receiving end, perform the opposite and bob's your uncle.

We do this all the time.

Shane.

09-23-2013 07:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Intaris that definitely is a step in the right direction, and will take care of most of our data types, but the "number to boolean array" node apparently doesn't support floating point.

Steve

09-23-2013 07:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Really? That seems like an oversight on the FPGA module side.....

09-25-2013 11:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

At this point we plan on converting to fixed point before converting to bit array for packing into the DMA.

09-30-2013 02:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm coming into this a little late, but just in case someone find this useful.

You can implement your own conversion to/from Single using an IP Integration Node. I have attached the code to do this and it should work on all platforms (although you may be asked to regenerate some files). The actual VHD behind the scenes is very simple since the flattened types have the same bitwidth (I chose to use U32 as the flattened representation).

library IEEE;

use IEEE.std_logic_1164.all;

entity ReinterpretType is

generic

(

kWidth : positive := 32

);

port

(

oldValue : in std_logic_vector(kWidth - 1 downto 0);

newValue : out std_logic_vector(kWidth - 1 downto 0)

);

end entity ReinterpretType;

architecture rtl of ReinterpretType is

begin

newValue <= oldValue;

end architecture rtl;

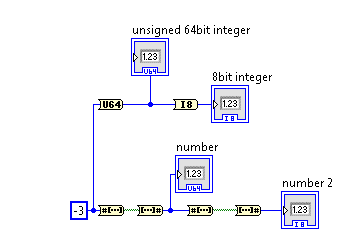

The IPIN usage looks like the following (fill in your code between the flattening and unflattening).

I've also attached a sample project for you to try out.

12-03-2013 02:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Intaris,

I'm finally implementing your suggestion. I assume you aresuggesting the lower path for encode/decode because it's cheaper on FPGA?

Thanks!

Steve

08-08-2024 09:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please kudo this idea to add support for bit reinterpretation (type cast) in FPGA.

- « Previous

-

- 1

- 2

- Next »