- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Labview FPGA FFT express vi latency.

Solved!07-24-2023 03:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I am optimizing some code that uses the FFT express VI. I need to process N number of windows of signal back-to-back. Meaning the next window comes right after the other. Of course I can't just feed this to the FFT when the previous window isn't done. So I have implemented some buffering. Also because these data pulses come in such often that I can't fully buffer the pulse using just one FFT because I don't have so much time. So I have opted to using 3 FFT algorithms which are used one after the other and when the last one has been used the next window is sent to the first FFT. These cause some issues with compiling because they take so much space and the timing is very tight at 200 MHz clock. I can get by with 3 FFT algorithms but preferably I would like to use only 2.

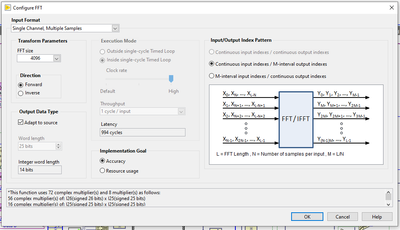

Here is my problem when reading the FFT Express VI documentation:

I am not sure how often the FFT is ready to receive data. The latency is 997 cycles and on the documentation it says

- Latency—Displays the number of cycles between the first point in the input frame and the first point in the valid output frame.

Does that also mean that I can start inputting new data after the 997 cycle, even though the FFT is outputting it's results still, or do I need to wait for that to finish?

Here's my FFT settings:

It says that to avoid data loss during calculation:

In a single-cycle Timed Loop, this Express VI does not accept or return values while computing the FFT. During this time, if the system or another node sends data to this Express VI, LabVIEW discards the data. This might happen if this Express VI receives data as part of a complicated or non-uniform pattern.

To ensure no data is lost, create a FIFO to hold data until this Express VI accepts values again. Ensure that the FIFO you create is large enough to hold all data points that collect during the FFT calculation time. To roughly estimate the size of the FIFO you need to create, divide the latency of this Express VI by the average system throughput.

If the FFT can receive data every 997 cycles I can get by with 2 FFTs but if it takes more time, then I need 3. I will appreciate all input you have to say to this.

Thanks:

Aarni

Solved! Go to Solution.

- Tags:

- latency

- throughput

07-25-2023 09:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would recommend to read through manual of LV FPGA as well as some online documentation for LV FPGA.

FFT Express VI configured for single channel, multiple sample can take samples every clock cycles. What you think is throughput and not latency. For the details and difference between throughput and latency, LV FPGA manual explains about them.

07-25-2023 11:11 AM - edited 07-25-2023 11:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for you input!

It seems that the FFT can take new data after the mentioned 997 cycles (so after the first datapoint comes out of the algorithm) and you don't need to wait for the data to "come out" of the FFT block first. I compiled the code with 2 FFT algorithms and it works fine and saves some compile time and probably some timing errors too... Seen as it now only takes 5 hours to compile insted of 7...

I am not sure what you are talking about but to my understanding, please correct me if I am wrong because I want to learn, latency is the time it takes the signal to travel through the given algorithm and throughput is how often it can receive signal. In my case the latency is 997 and throughput is 1 sample vector / tick. What I was asking about is the "throughput" of the whole FFT calculation. From the first input vector put into the FFT at constant 16 samples/tick speed is the FFT able to receive new data to calculate the next window. In this case it seems that that "throughput" is 997 cycles from the first data vector going in to the algorithm.

Excuse me for my confusing wording. I am not good at explaining things and it is even harder to explain things in english.

Aarni

07-25-2023 08:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You don’t have to wait for the first window to be done, before feeding next window to the FFT block.

In other words, the FFT block handles calculations over multiple windows at the same time.

07-26-2023 05:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Okay...

But it says on the documentation:

"Avoiding Data Loss During FFT Calculation

In a single-cycle Timed Loop, this Express VI does not accept or return values while computing the FFT. During this time, if the system or another node sends data to this Express VI, LabVIEW discards the data. This might happen if this Express VI receives data as part of a complicated or non-uniform pattern.

To ensure no data is lost, create a FIFO to hold data until this Express VI accepts values again. Ensure that the FIFO you create is large enough to hold all data points that collect during the FFT calculation time. To roughly estimate the size of the FIFO you need to create, divide the latency of this Express VI by the average system throughput."

07-26-2023 08:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That statement applies only to the case of When Throughput is Not Equal to 1 cycle / input.

When multiple samples input mode is selected, throughput is forced to 1, and ends up with using a certain amount of resources to accept new samples for all the time. Please carefully read documentation and test in simulation mode before wasting so much time like 5, 7, any hours.

it would be better not to mark a wrong post as a solution, by the way.

07-26-2023 08:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for clearing that up. If you haven't picked that up I am very new to this LVFPGA stuff. I have read the documentation many times but I have difficulties understanding it.

I found that in simulation mode FFT latency would not be consistent and I didn't trust it's ability to accurately tell me how the code would work. But that is probably my mistake too.

I marked my comment as solved because at that time I thought that I had figured it out and tried to explain my solution. I of course was wrong...

I am sure you are frustrated by my idiotic posts...

Thanks again

Aarni

07-26-2023 11:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No no, I wasn’t frustrated. just wanted you to try things by yourself not to waste your time and others. Keep it up!