- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 9401 10 uS (microsecond) Digital Write and Read with LabVIEW FPGA

Solved!09-16-2019 10:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All,

I hope that everyone's having a great day so far. I would like to check with I am currently working on and the issues.

I have designed a quite simple project with FPGA.vi and RT.vi, with NI-9401 for 3 Digital Write (DO 4-7) that delays for 10 uS, 20 uS and 30 uS. Within the same FPGA.vi, I also would like to read them (DI 0 - 3)

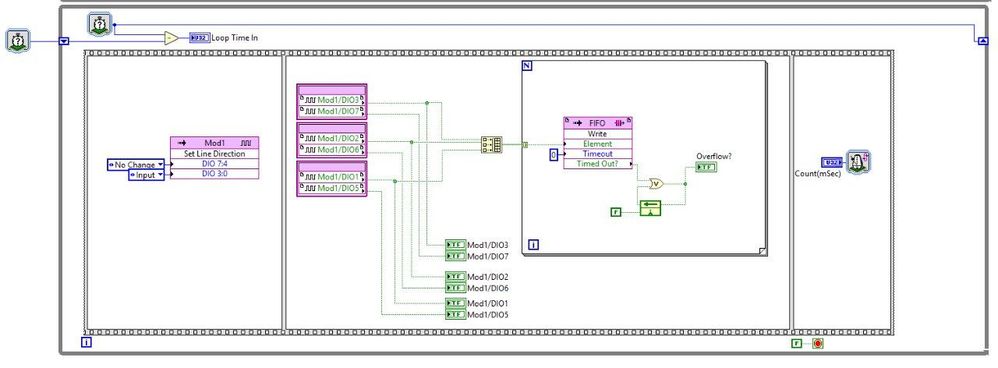

Previously, this FPGA.vi works for the order of 10 ms, 20 ms and 30 ms with this read loop section of the code

Along the way, I noticed that this while loop at the FPGA is simply couldn't afford to be in the uS order (I believe when I benchmark it, I got 4159 tick counts per loop or about ~100 uS) so I reckoned that I need to resort SCTL.

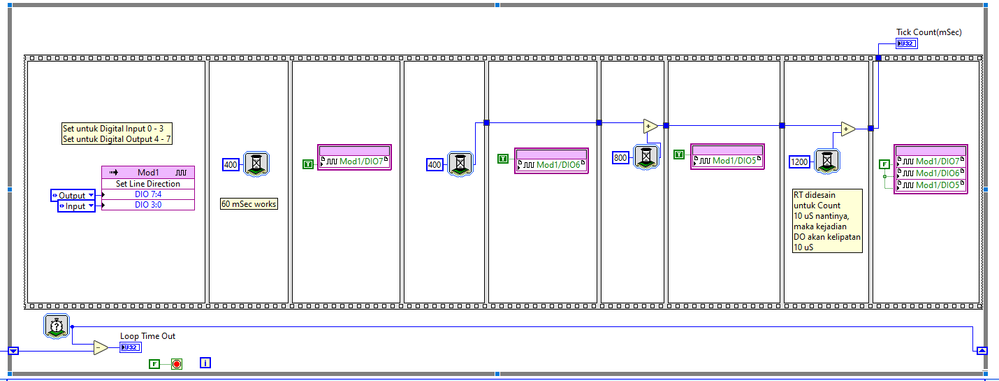

My challenges were on how to adapt on this SCTL as I realized that I couldn't use the for loop and directional within the SCTL. After trying to adapt it, I came up with this

Ultimately, what I am trying to confirm are:

- Did my approach was right? (using SCTL on only read, pass it to another loop by converting the Boolean to U8 and transfer them to another FIFO)

- If so, I am unsure on the rate of the Digital read itself - does the DI read at 25 ns (since benchmark result of 1 tick), 100 ns (since 9401 only support up to 100 ns) or 1,5 us (since the transfer loop result on 60 ticks)

- Do we have the example of my application on this (reading 10 us digital inputs)

Really appreciate your time and resource on this. Wishing all a great day ahead.

Solved! Go to Solution.

09-17-2019 02:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Fareed17,

If you were able to compile the code, the SCTL will run at 25ns and will attempt to put data to the FIFO at that rate (If the maximum DI update rate is less than that, the DI read node might return repeated values). Probably there is an overflow happening at the Digital Convert FIFO, if the reading of this FIFO occurs only at 1.5us rate. You can confirm this by checking the 'Timed out?' flag of the Write node (which is presently unwired).

Although SCTL is a good way to optimise, here it results in oversampling and overflow because the write rate is much faster than the read. I feel that in this case you can achieve the DI read rate under 10us, using a normal while loop and by properly pipe-lining the DI read and FIFO write. You can find LabVIEW examples on how to do this.

09-18-2019 02:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ArunJ,

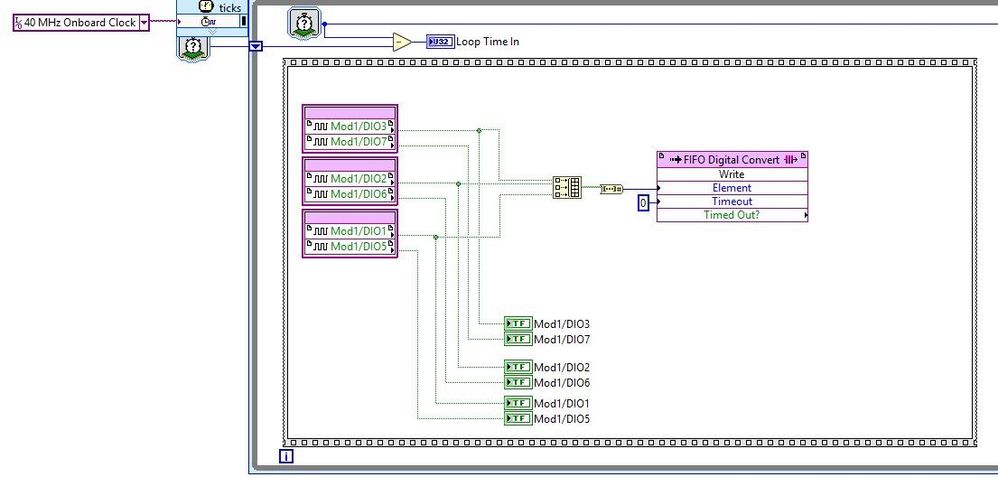

Really appreciate your shared thought on this. I have examined the pipelining option and applied it to my first version of the LabVIEW FPGA code.

It works wonders! My read loop now iterate for about 24 ticks (0,6 uS), more than enough for NI-9401 as I managed to read the data in the order of 10 uS.

One thing that I realized, I was wondering on is it possible for us to alter the loop rate of this loop? I was experimenting on using the loop timer though it seemed that it would mess the data read.

The reason I ask this is because I would like to use later on NI-9425 that has slower update rate at 7 uS.

Thank you for your help on this and hope that you are having a great time ![]()

09-18-2019 03:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

HI Fareed,

You should be able to change the loop rate. In fact, it is using the loop timer, you should set the desired sampling rate for a module, unless it is a Delta sigma module.

Using the loop timer will not affect your data read. There is no use in running the DI read loop faster than the the update rate of DI module.

09-18-2019 09:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Arun,

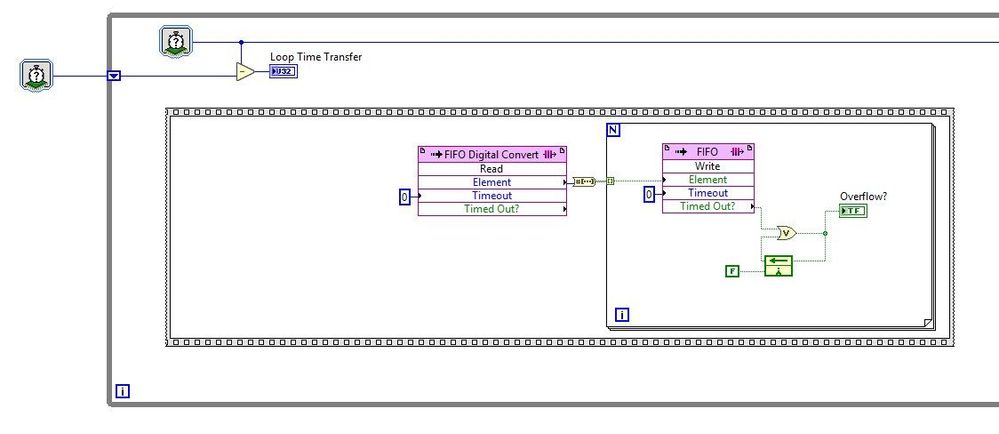

Thank you for clarifying my doubts. I had used the loop timer within my While Loop read in combination with the FS structure.

The code now works as expected. Really appreciate your thoughts and discussions. ![]()