- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with transferring information from FPGA to RT

Solved!09-17-2019 05:22 PM - edited 09-17-2019 05:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have problems transferring information between my FPGA code and RT VI.

I am using an ultrasonic sensor to measure the distance between my robot and an object, and the loops work very well, the problem is when I try to bring the information from the FPGA to the RT, the motor circuit just doesn't work anymore.

I already tried using a method with DMA FIFO to see if it improved, but got the same results.

I noticed that there is a big decrease in the number of iterations in the loop where the motor is programmed compared to the loop where there is no sensor data acquisition.

I don't know if this could be the problem or if there is an error in the code. Anyway, if anyone can help me, I will be extremely grateful

If you need more information, feel free to ask me

I attached my 3 VI's

One is motor control without ultrasound

And the other is the engine control with the ultrasonic

You can then test them individually to see if the same problem happens.

I am using MY-RIO1900 with LABview 2019

Solved! Go to Solution.

09-18-2019 05:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I can't see you code on this machine, but I might be able to provide some philosophical support...

I would like to clarify your setup: You have a sensor connected to the FPGA, you collect and process data there and use it to control a motor circuit that is also connected to the FPGA. You now want to transfer the data to the RT, and now control the motor circuit with the RT. But you find that the data transfer is very slow so the RT does not tell the motor where to go next fast enough.

I have some questions:

- How did you transfer data before using the FIFO? I guess using a front panel control?

- How much data do you want to transfer? is this raw data or processed data?

You should process on the FPGA and then transfer the positions to the RT. Depending on the application, I would use a front panel control for this. Since I assume that the motor circuit updates much slower than the FPGA.

09-18-2019 07:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Gabriel.Leonardo wrote:

I noticed that there is a big decrease in the number of iterations in the loop where the motor is programmed compared to the loop where there is no sensor data acquisition.

How much is the difference that you see in the loop rate, with and without the FPGA read loop? You can get that information by checking the output node of the Timed while loop.

I see that you want to keep the loop rate as 10ms (For this, the 1KHz clock source is enough, in stead oh 10MHz).

Also make a note of how much is the CPU usage in the cases of with and without the FPGA read loop.

Since you have tried the DMA also, I would like to know how you have read the DMA. Was it the Polling or Interrupt based?

09-18-2019 11:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Max

Almost that, I'm collecting sensor information through the FPGA but my motor is controlled by RT

I need to transfer data from FPGA to RT to set a minimum distance the robot can reach from some object, When I do this with open fpga reference, the engine loop no longer works and after checking it out, I find that iterations fall a lot and thought this could be the cause of the problem, but I don't know what causes this iteration crash

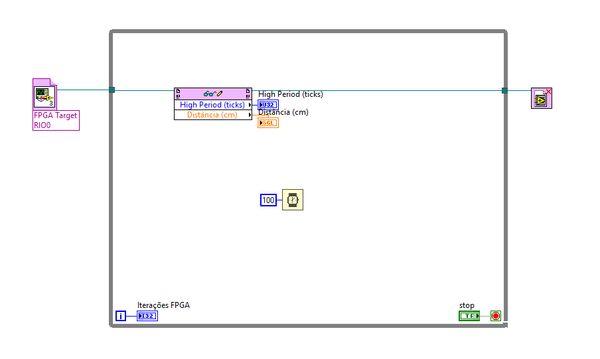

Regarding the transmission method, I used the open fpga reference, as shown in the image below.

About the data, it is being processed by fpga and I just need to send it to RT to continue with the program.

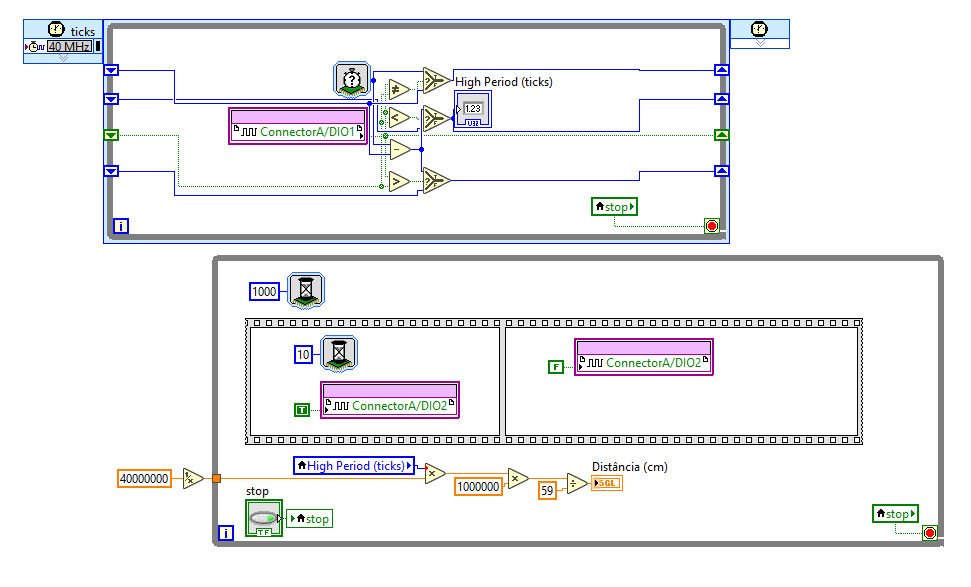

The image below is the program made in FPGA

09-18-2019 12:08 PM - edited 09-18-2019 12:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Arun

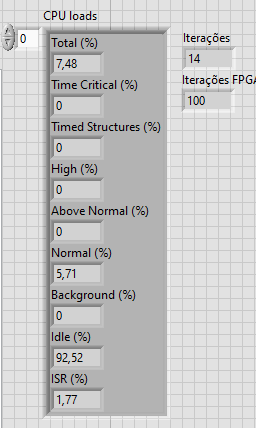

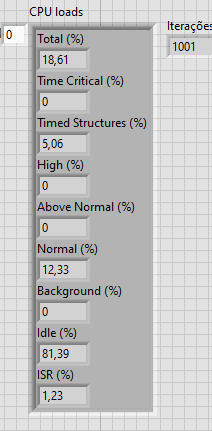

I don't know if this is the best method to test but, I put a timer that after 10 seconds turns off all my VI and I got this information from the CPU and iterations

This image is from the loop with the FPGA

And this is the loop image without the FPGA

In the loop without FPGA I got 987 more iterations, that's the difference I noticed between the two circuits but I'm not sure this is the problem that is not letting my motors run.

The period is the same for both circuits. (I'm using 1MHz clock source)

About the loop rate, thanks for the tip but when I modified the VI, my encoder didn't work correctly, I will check it later

Am I missing processing or something like using 1MHz instead of 1kHz?

About FIFO, I don't remember seeing methods like Polling or interrupt based, I used FPGA FIFO, I don't know if there is any difference between this and RT FIFO.

The image below shows the FIFO I'm using.

09-19-2019 05:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

The images are not loading. Can you attach them again and re-post?

By the way, you can also refer to the links below, regarding DMA usage and CPU overhead.

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000P9SASA0&l=en-IN

https://forums.ni.com/t5/LabVIEW/FPGA-to-Host-best-data-transfer-method/td-p/428523

09-19-2019 11:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

These are the images that was placed in the answer above. I will take a look at these links, thank you very much. If all goes well I will attach your answer as correct.

09-20-2019 10:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I found the answer !!

The problem is that my FPGA code was coming into conflict with the FPGA code that MYRIO has already integrated.

To get around the problem it is necessary to redo the code and reference this custom bitfile at the beginning of main VI.

Thank you for taking the time to help me.