- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Pulse duration in labview FPGA

Solved!02-21-2014 06:03 PM - edited 02-21-2014 06:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear

can one help to built a lv FPGA to measure the pulse duration

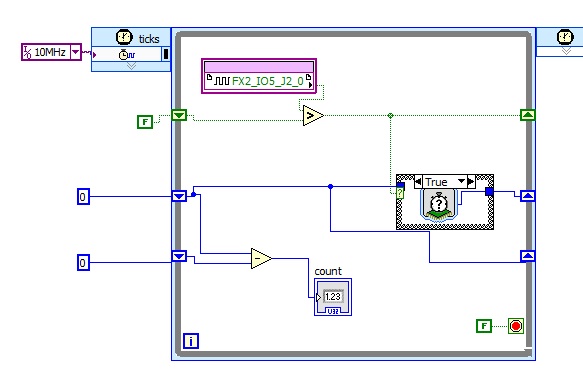

my first start lv VI is shown below for Spartan 3E kit the but its fail to work

is thei rany modify make it work??

for the case structure in false case the old value is moved instead of tick counter

best regards

Solved! Go to Solution.

02-24-2014 05:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey mangood,

Do you just want to count the number of ticks that a Digital line remains high and then output the result?

Regards,

Ryan

CLA

02-24-2014 05:34 PM - edited 02-24-2014 05:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Ryan-P wrote:

Hey mangood,

Do you just want to count the number of ticks that a Digital line remains high and then output the result?

Regards,

Ryan

i want number of ticks that a Digital line remains high and number of ticks that a Digital line remains low

and can work for long time for more than 1 hour

02-24-2014 08:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Get rid of the boolean shift register and the timer function inside the loop. Just have two shift registers one for the high count, one for the low count. If the Digital Input is True, then increment the High shift register. If it is False, increment the Low shift register.

02-24-2014 08:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Like RavensFan mentioned, the simplest way is to use a pair of shift registers and record two of the following three: cycles high, cycles low, or total cycles. Increment the value that is currently active based on the I/O value.

What is the expected pulse/cycle rate of the signal? You mentioned reading for over an hour, do you need to have exact values for verifcatoin, a rolling average of pulse counts, a median value, etc. All of these can change how you store and process the results.

02-25-2014 08:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

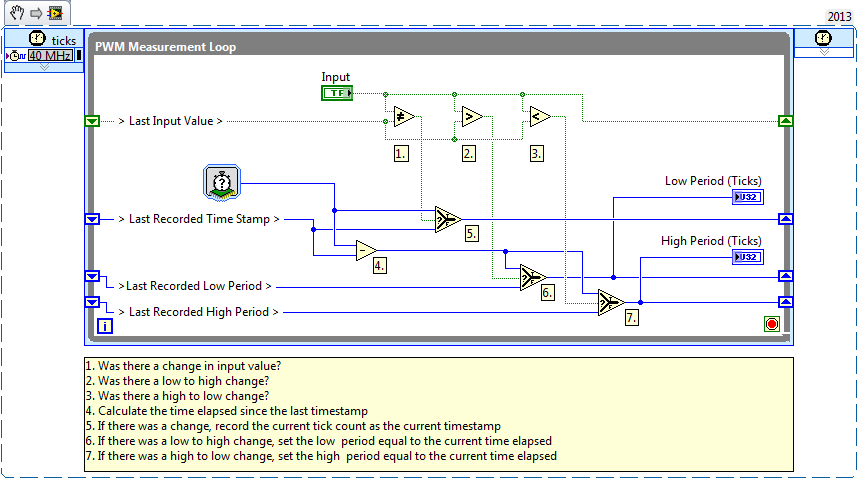

There is also an Example in the NI Example finder on exactly how to do this![]()

You can search for Pulse Measurement to find it, or use the snippet below:

TJ G

02-26-2014 09:28 AM - edited 02-26-2014 09:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

dear

thank you all for the replay

i will use the NI Example for test

i think the iniail problem of such VI is the timer wraps to zero. If this timer will work under 40MHZ source clock

how long is the timer will be work without wraping??

back again after test

best regards

02-26-2014 02:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

40MHz inverted is 0.000000025 This is how many seconds a single tick takes. If your tick counter is a U32 (the largest it goes to without extra work) you have 2^32 values which is 4294967296. Multiply these two numbers and you get 107.3741824. This means after 107 seconds your U32 counter will roll over. For this to work long term you will need some way of keeping track of the amount of time passed. I've seen some example 64 bit counters here, or here.

Unofficial Forum Rules and Guidelines

Get going with G! - LabVIEW Wiki.

17 Part Blog on Automotive CAN bus. - Hooovahh - LabVIEW Overlord

02-26-2014 03:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Using a U64 will work just fine for you. It won't roll over for about 14,600 years give or take a couple decades. I'm using a 64-bit value in my FPGA application. I don't think I need to worry about it rolling over.![]()

02-26-2014 03:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Just found an Idea Exchange post asking for a 64bit counter for FPGA.

Unofficial Forum Rules and Guidelines

Get going with G! - LabVIEW Wiki.

17 Part Blog on Automotive CAN bus. - Hooovahh - LabVIEW Overlord