- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Reading FIFO's in SCTL does not work as a FIFO

Solved!03-18-2019 12:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I hope this is enough, if not can i post some simple VI's tomorrow.

I have a weird behaviour in my SCTL when reading two instances of the same FIFO, which is set to "never arbitrate".

Below

Im sending an array into the FIFO, for example

fifo_array = [0, 0, 0, 0, 0, 0, 1]

Below i have posted two ways of extracting the array, where i am gathering the data in some fixed arrays of size 4.

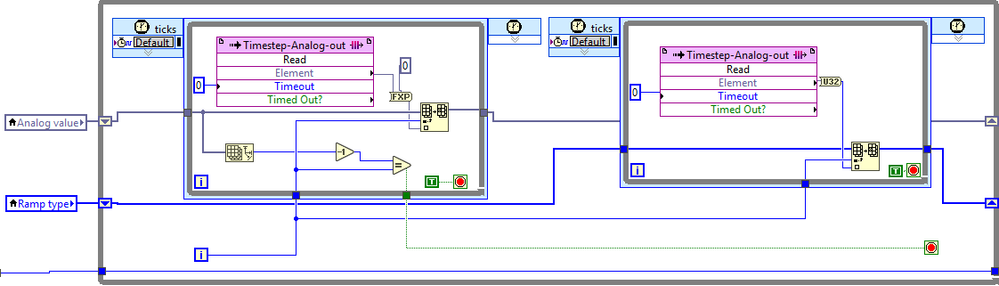

Optimal readout which should work, but doesn't:

Return value of analog value = [1,1,1,1]:

Does work:

return value of analog values = [0,0,0,1]

Is there any obvious reason for why this should not work ?

Solved! Go to Solution.

03-18-2019 02:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I don't think you could do two FIFO reads in a single cycle, can you?

(I don't do much FPGA.)

Try reading two elements at once instead of reading one element twice.

03-18-2019 04:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That would explain it, i just thought that LabVIEW would complain when i try to compile it.

When you say "Try reading two elements at once instead of reading one element twice.", do you mean pipelining or is there some way that i can read two elements at once ?

03-19-2019 04:56 AM - edited 03-19-2019 05:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You need to check the "Timeout" flag. The FIFO simply returns the last value on a Timeout. If you want to avoid this, then you need to make sure you parse the "Timeout" output of the FIFO accordingly. That could be one problem.

Any reason why you're sending 7 elements per FIFO and reading 8?

The second is that we have no idea how you're filling the FIFO...... So your statement "This should work" cannot be verified. It also seems like a really weird way of parsing data from a FIFO. Can't you just use a single "Read" primitive and wire the output to a case structure which alternates between the two arrays?

03-19-2019 06:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Any reason why you're sending 7 elements per FIFO and reading 8?

That a mistake, i am sending 8 elements per FIFO

Fifo_write = [0, 1, 2, 3, 4, 5, 6, 7]

Im filling the FIFO with the help of NiFPGA in python:

https://github.com/ni/nifpga-python

After the FIFO's is loaded the FPGA-target-VI runs.

Can't you just use a single "Read" primitive and wire the output to a case structure which alternates between the two arrays?

Yes, i don't know why i did it like this, thank you!

This clearly improves it, but just to be sure, is it theoretically possible to read two instances of the same FIFO in a SCTL ?

03-19-2019 07:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

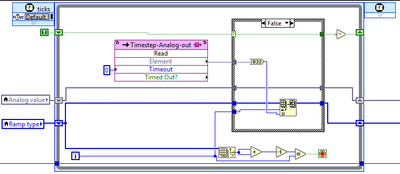

This is not an answer to your question, but in your second screenshot you are missing a data flow dependency between your two SCTLs, so there is no way to predict which loop will execute first. Since this code runs on a FPGA it will probably run in parallel.

Regards, Jens

03-19-2019 07:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thankyou, that was the problem i was having at the moment!

When i rearranged i forgot to put a wire between the FIFO's to force dataflow.

03-19-2019 08:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So are you saying you have your screenshots reversed? Did the one with the sequence structure work but the one with embedded SCTLs work? I ask because I understood the opposite from your post.

03-19-2019 10:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry, i was a bit to fast in posting my question.

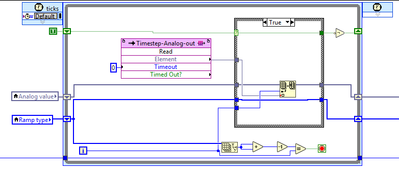

1. The screenshot without the sequence structure, so the one with two SCTL is the one that works.

2. There is a fault in the screenshot, there is supposed to be a wire connected from the first FIFO's reference out to the second FIFO's reference in. that is to ensure dataflow.

I have restructured my loop like this for now (Which works).