- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Simulating input on a Flexrio PXIe-5774

Solved!06-04-2023 04:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

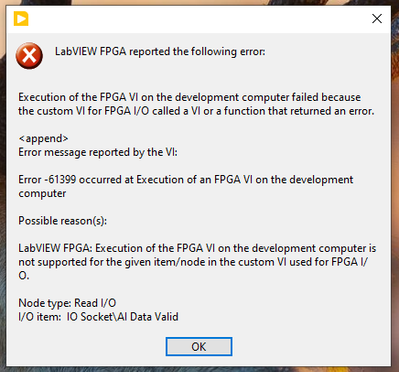

I am programming a PXIe-5774 FlexRIO FPGA. Since the compilation times are huge, it would be helpful to be able to simulate the FPGA VI on the host computer before compiling. For that I would need to simulate fpga input.I created this VI from template to simulate input but I am not understanding how that is done. I tried to follow the instructions on (https://www.ni.com/docs/en-US/bundle/labview-fpga-module/page/lvfpgaconcepts/test_bench_tutorial.htm...) but whatever signal I put into the "Read I/O" -Case Structure running the FPGA vi in simulation mode produces this error:

I struggle to find instructions on what to do. I have attached the signal simulation code and the default personality vi that comes straight from labview example finder.

Is this signal simulation possible on my fpga configuration? Is there some other way of simulating signal so that I don't have to compile and hope for the best?

Thanks very much:

Aarni

Solved! Go to Solution.

06-04-2023 07:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would remove the AI terminals and add a Host to Target FIFO.

The link mentioned may only work for some NI FPGA cards such as R Series.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

06-04-2023 09:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, this tutorial is obsolete way back almost 10 years ago. Below may be the main method for LabVIEW FPGA simulation.

Testing and Debugging LabVIEW FPGA Code

As for how to simulate hardware input, it would be better not to use I/O nodes directly. Rather, switch using something diefferent signal source by replacing I/O nodes with Conditional Disabled Structure. Example of doing this is shown in Sample Project of Reconfigurable Oscilloscope.

Add Custom FIR Filter in FPGA of Reconfigurable Oscilloscope

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA03q000001DtswCAC&l=en-US