- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Tick Count Express VI outputs '0' on FPGA target running with Simulated I/O

Solved!09-03-2014 07:58 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When I set my target to "Execute VI on Development Computer with Simulated I/O", the Tick Count VIs all output '0 every time they execute. How can I get them to output a progressive count (in the "ticks" instance) or a proper timestamp (in the "ms" instance)?

Solved! Go to Solution.

09-04-2014 02:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David_Staab,

What value do you expect from the Tick Count Express VI and can you share a code snippet or the code that shows that the Tick Count Express VI only outputs 0?

Also, what version of LabVIEW are you using?

Starting with LabVIEW 2013, the Tick Count Express VI uses simulated time rather than real time, when executing your FPGA VI on a development computer with simulated I/O. You can find more information about this in the Version 2013 Features and Changes (FPGA Module) help documentation.

Regards,

Applications Engineer

National Instruments

09-04-2014 03:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm using LV 2013 SP1.

You want an example VI? Put the "Tick Count" VI in a While loop and connect an indicator to its output. You'll see '0' on every iteration when you run it under simulation.

The value I expect is a progressive count (in the "ticks" instance) or progressively incrementing "simulated time" (in the "ms" instance), both with rollover.

09-05-2014 10:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

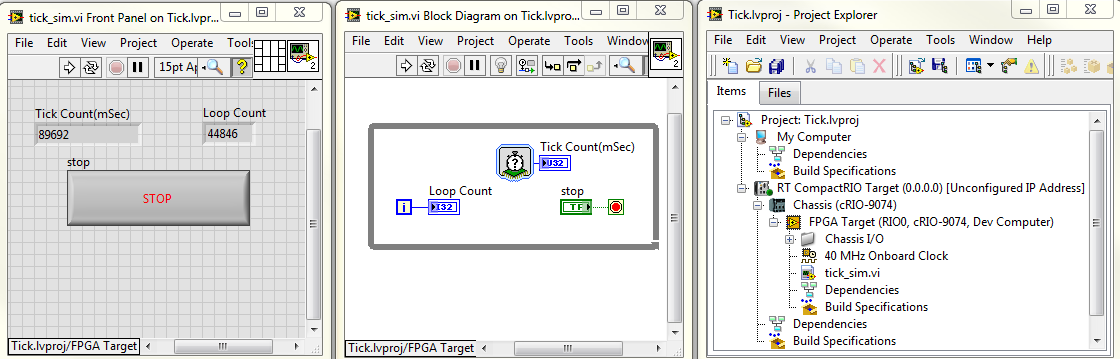

I used LabVIEW 2013 SP1 and I was unable to reproduce this issue on my end. The screenshot below shows my result.

As shown on the Front Panel, the output from the Tick Count Express VI was not 0 on every iteration of the loop.

To make sure we are comparing the same code, can you reproduce this issue with the Tick Count shipping example? You can find this shipping example in the Toolkits and Modules>>FPGA>>CompactRIO>>Fundamentals>>Clocks and Timing>>Tick Count section in the LabVIEW Example Finder.

Regards,

Applications Engineer

National Instruments

09-05-2014 03:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Oh. Change the While Loop to an SCTL. Sorry.

09-05-2014 04:07 PM - edited 09-05-2014 04:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm unable to reproduce this issue with the Tick Count Express VI in the a Single-Cycle Timed Loop. The screenshot below shows the result, on my end.

Would it be possible for you to share the code that reproduces this issue on your end?

Regards,

Applications Engineer

National Instruments

09-07-2014 04:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually it does work as expected. I apologize. When in [ms] mode it ran so slowly that my test VIs looked like they were failing and I didn't notice the value incrmenting when I probed it. I changed the test to use the [ms] instance when running on the FPGA and the [ticks] instance when running with Simulated I/O. This looks like it gives 1 tick every "simulated millisecond" when simulating, and my tests work fine now.

Thank you for the help. Sorry again for the false report.