- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Trying to generate a clean square wave on FPGA

04-23-2020 04:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am using a PXI-7842 FPGA module. I'm trying to output a 10MHz square wave on one of the DIO channels. I am using the Square Wave Generator VI from the FPGA Functions pallet. I get a somewhat decent square wave up to 1MHz, but at 10MHz, it's a sawtooth wave form. I am using the FPGA's onboard 40MHz clock. How can I get a cleaner waveform? Or are there frequency limitations?

04-23-2020 10:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well, it's either your hardware, your software, or your "measurement-ware" (meaning how you are measuring the square-wave output from the FPGA). It's hard to comment on your software (we can guess, of course). Find a good engineer, take her to your setup, and show her the problem, sharing your code with her -- she'll probably find where the problem lies.

Bob Schor

04-24-2020 10:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What cable configuration and length are you using between the hardware.

Could potentially be excess capacitance in the setup causing the square wave to degrade.

But need more details to ascertain the root cause.

-AK2DM

"It’s the questions that drive us.”

~~~~~~~~~~~~~~~~~~~~~~~~~~

04-24-2020 11:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

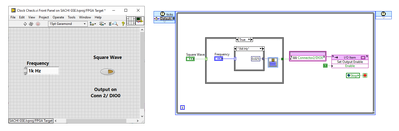

Here is the code I'm using. I've also attached a copy of the VI. It is a fairly straight forward program. I'm simply using the supplied function "Generate Square Wave.vi". I've also attached pictures of the waveforms, using a Tektronix TDS 3034 oscilloscope.

04-24-2020 12:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The cable is the standard NI cable.... 1 meter.

04-25-2020 10:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you checked your scope probe? There should be a place on the scope to hang the probe and have it "see" a "calibration" square wave, where you can adjust the capacitance of the probe to get clean square waves. Also, is the scope probe ground connected to signal ground?

04-27-2020 02:56 AM - edited 04-27-2020 03:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Creating the 10 MHz Signal in a FPGA is simple, just toggle a value with 20 MHz 🙂

And now: Wellcome to the analog world 😄

There is a long, never ending 😉 discussion on how much bandwidth you need. ... Infinity in theory ... 20 times the base frequency is a usual pratical value ... .

If you show that signal by hand you will find that as higher the frequncy goes, as more force you need.Newton law (F=ma)

Sort of same for the analog signal. (and even for the 'analog' digital memory cell in the FPGA ) .. to make it faster you need to make it smaller, reduce the amplitude or you need more energy for switching 🙂

That you see a sawtooth is a strong indicator for limited slewrate (limited force) . If you look closer to your slow signal, I bet you find about the same slewrate there.. So too much load at your signal output (or your scope isn't fast enought.. but this kind of problems vanish nowadays) . Fast Probes that don't put to much load on a signalsource is still a common problem.

Try an active (expensive) FET- Probe or a correctly compensated 10:1 probe ..

A 10:1 probe has a 9M resistor at the input in parallel with a smaller capacitive load (ten times smalller than your scope input)

Or put more force on the output: Use 4 or 8 outputs in parallel .. but still build a correct termination (here I simplify .. i have no information on the sourceimpedance of one output)

Henrik

LV since v3.1

“ground” is a convenient fantasy

'˙˙˙˙uıɐƃɐ lɐıp puɐ °06 ǝuoɥd ɹnoʎ uɹnʇ ǝsɐǝld 'ʎɹɐuıƃɐɯı sı pǝlɐıp ǝʌɐɥ noʎ ɹǝqɯnu ǝɥʇ'