- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Type of the source is void while importing external IP

12-16-2013 05:10 PM - edited 12-16-2013 05:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Absolute beginer (about ~10 hours in) trying to instantiate an external VHDL IP on a FPGA target. I followed this technical note up to the point where I tried to connect an output port of the IP to a led. Connecting both always trigger the same error: The type of the source is void. I believe that the port is defined properly in the CLIP:

<Signal Name="outLed">

<HDLName>outLed</HDLName>

<Datatype>

<Boolean/>

</Datatype>

<Direction>FromCLIP</Direction>

<SignalType>data</SignalType>

</Signal>

Which I believe matches the VHDL entity:

entity IPNode is

port(

ap_clk :INSTD_LOGIC;

ap_rst :INSTD_LOGIC;

ap_start :INSTD_LOGIC;

ap_done :OUTSTD_LOGIC;

ap_idle :OUTSTD_LOGIC;

ap_ready :OUTSTD_LOGIC;

outLed :OUTSTD_LOGIC);

end;

For the record I use Labview 2013 and I'm targeting the Zynq Z010 on a MyRIO.

12-16-2013 06:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Just one small precision. I used CXG to generate the XML CLIP.

12-17-2013 12:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

>> I followed this technical note up to the point where I tried to connect an output port of the IP to a led. Connecting both always trigger the same error: The type of the source is void.

Do you have a screenshot of the error? When did it happen, during FPGA compilation or when you ran it after compilation? Are you trying to connect the output of an IP to FPGA pin? If so, you should do this via a Socketed CLIP.

12-17-2013 07:18 AM - edited 12-17-2013 07:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

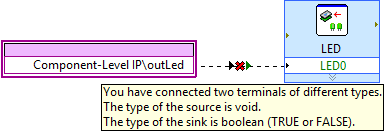

Here's the screenchot:

It's happening while I'm drawing the net. The output of the FPGA is meant for another vi (Led).

12-17-2013 07:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This screenshot is kind of confusing, since CLIP is only intended to be used under FPGA while the LED express VI is to be used on RT. I'm not sure where you are drawing this. However, it seems that you will need to use variable to pass CLIP output to RT before feeding it into LED.