- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why is output signal pulled high when stopping program in RT

Solved!10-30-2014 11:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm using 9401 to output a PWM signal. When I run the FPGA program and stop it, nothing unnormal happens. BUT when I run the program through RT using the compiled bitfile and stop, there will be a high level about 110ms.

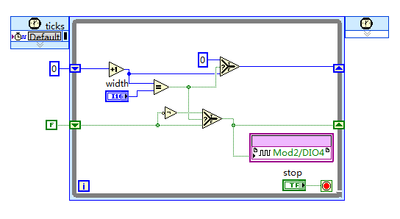

Here are my FPGA and RT block diagrams of a simple signal output.

I wonder why this could happen? Should I notice any specific when programming the RT?

Thanks in advance

Solved! Go to Solution.

10-31-2014 04:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You might want to add some logic to make sure that output goes low when the stop is set to TRUE inside of your Single Cycle Timed Loop. My guess is that you are just seeing a delay between when the FPGA is commanded to stop and when the bit file is actually closed and the FPGA is reset.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

10-31-2014 06:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your kind reply

Finally figure it out

According to your statement, I viewed the help. There is indeed a reset. I can discard it by right clicking the 'close FPGA VI reference', which needs to add additional logic to set output low in FPGA program