- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

"nilvfpga_acknowledger_Spartan 3ُE is missed +labview fpga +spartan 3e

Solved!04-12-2013 03:51 PM - edited 04-12-2013 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

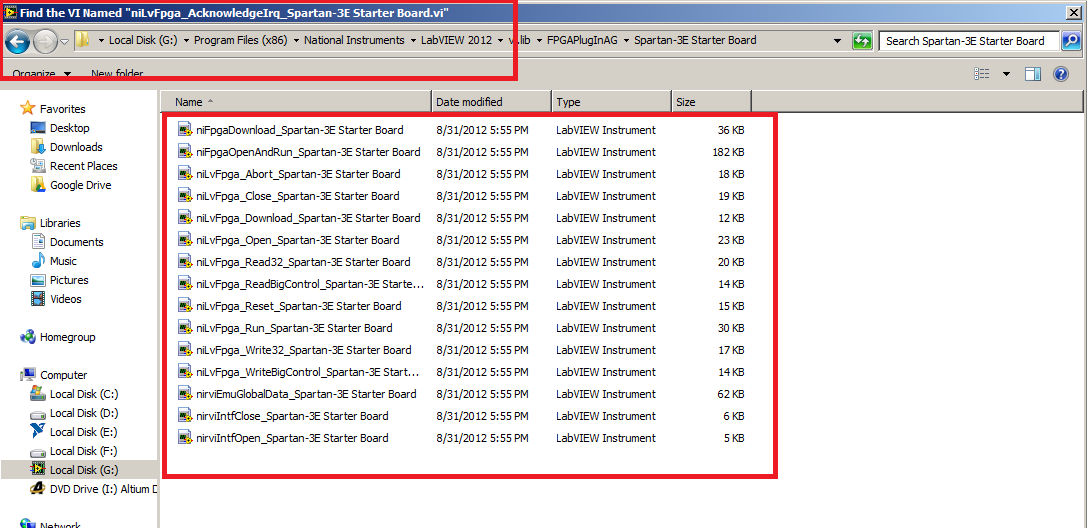

during work today I find that this file """nilvfpga_acknowledger_Spartan 3ُُُ"""" is missed from ""support files"" that AVAILABLE for Spartan 3E in labview 2012 sp1

DOSE ANYONE HAVE IT!???!! Please

I think the position of this file as in figure below

best Regards

Solved! Go to Solution.

04-12-2013 06:18 PM - edited 04-12-2013 06:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

HI NI:::

please read this replay carefully

for above missed file I search for this file in another palace and I find this file niLvFpga_AcknowledgeIrq_PCIe-8237R and this niLvFpga_AcknowledgeIrq_Dynamic

I open it and I can see that both same structure so I used them to slove problem above

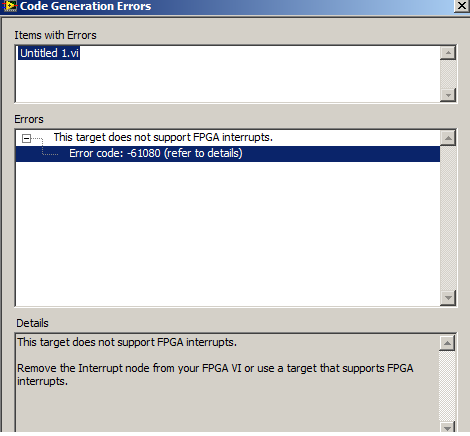

after that this error appear to me in compilation process

This mean that the Spartan 3E does not support interrupt operation in labview fpga

I was suppressed .....Do you now why because I learn from LabVIEW FPGA Training Spartan 3E that Spartan support this operation

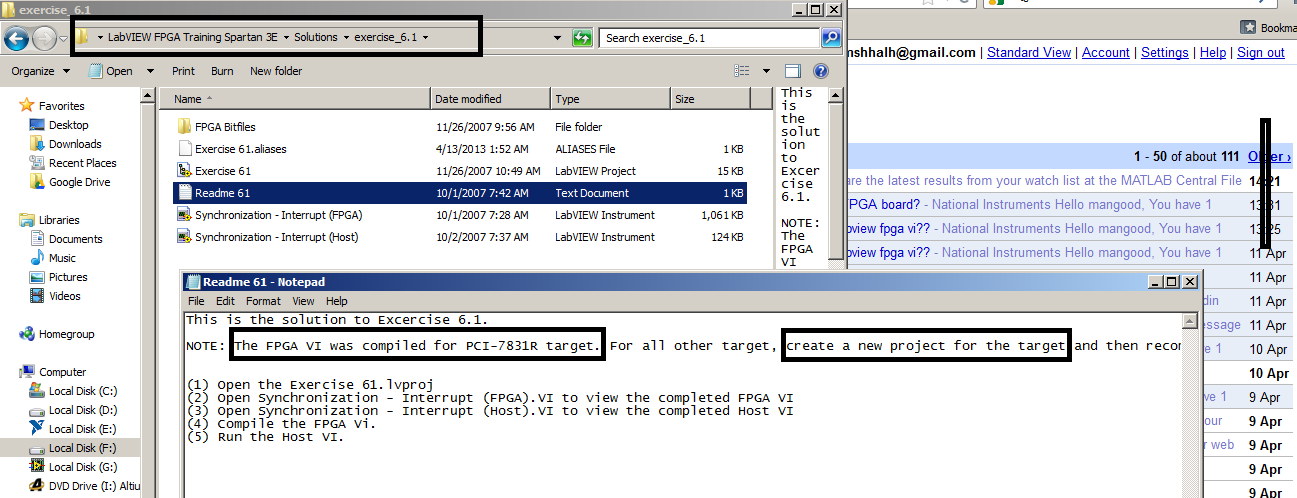

but when take in depth ......

Oh you can see in tutorial the completion was for pci not Spartan and the tutorial for Spartan !!!!!!!!!!why this why

in same figure

note what he say ""another target "" this mean for example ""spartan""

why this conflict

04-15-2013 12:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi mangood,

What device are you trying to compile code onto? Is it a PCI 7831R?

You can see in the document linked below, that the PCI 7831R actually uses a Virtex-II chip, not a Spartan 3E chip.

http://digital.ni.com/public.nsf/allkb/ED6FC9CF7B983CFD86256DCE0072E313?OpenDocument

Regardless, the 7831R device does support interrupts, so if that is the device you are compiling to, you should not be having a problem. To determine whether a target supports interrupts, access the FPGA Target Properties dialog box and locate the Target Information section of the General page. For instance, on the Properties page for the PCI-7831R, I see "Number of Logical Interrupts: 32"

National Instruments

04-15-2013 12:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

04-29-2013 03:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As you have already discovered, you cannot use IRQ synchronization for these targets. There are mechanisms that you could use to ensure that there is some synchronization between the two sides of your application, for example using the fact that you can read and write to either a control or indicator and do so from either the host or the FPGA. For example, you could do the following:

- From the host, write a control to "tell" the FPGA to do something.

- On the FPGA VI, wait until the control changes to your expected value that you wrote in 1.

- Once you've done something on the FPGA, to indicate back to the host that something has been done, change the value of the same control in 1. (or it could be a different control/indicator)

- On the host, once you've done the work in step 1., have it periodically check on the control (or a different control/indicator) to be changed by the FPGA to indicate that some work has been done

This is a simple synchronization mechanism known as "polling". Unfortunately, due to technical limitations in the communication interface between the host and the FPGA for these targets, interrupts are not available to use.

11-10-2014 02:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sir,