- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DRAM model behavior

03-07-2013 08:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

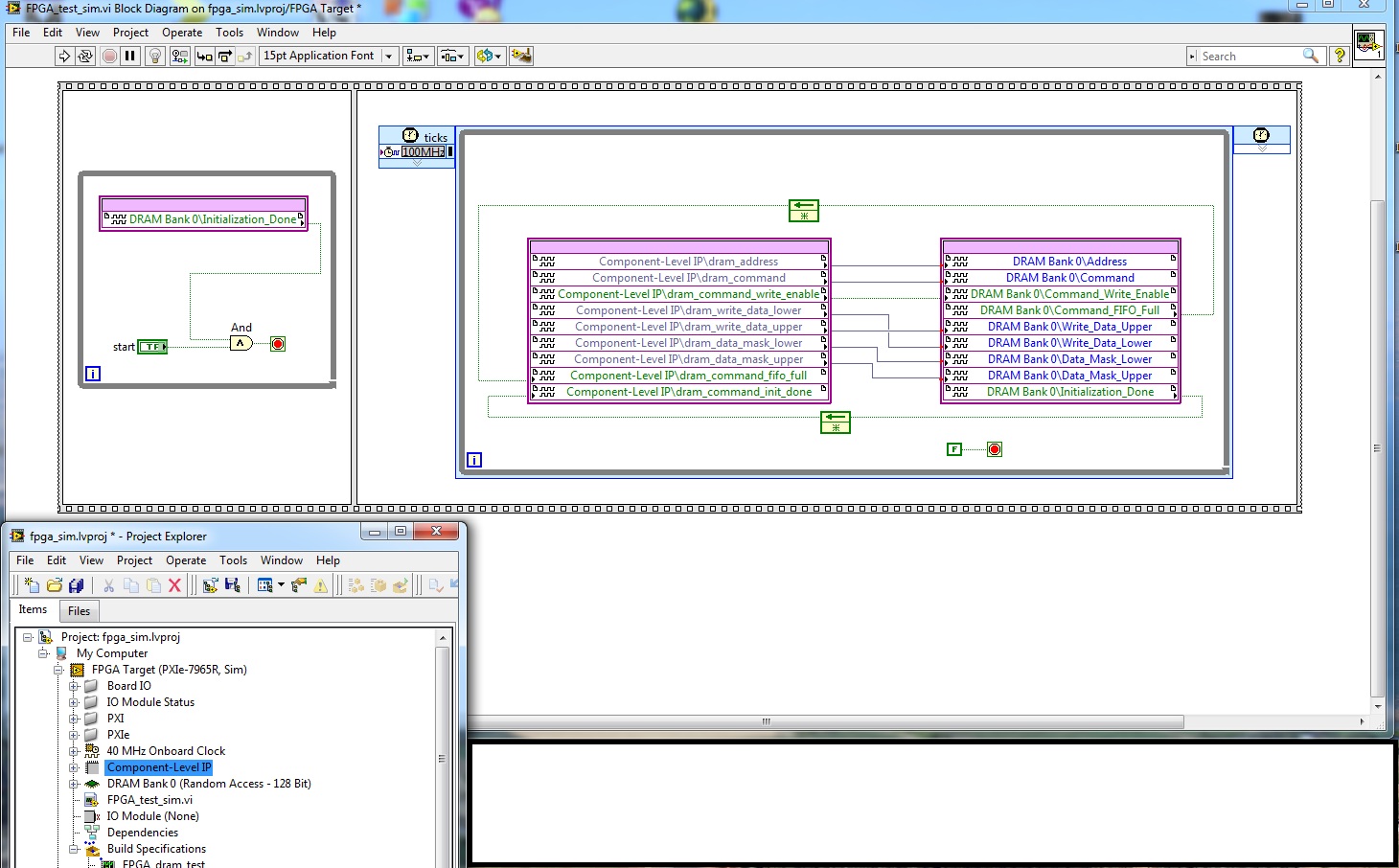

I am trying to simulate socketed DRAM CLIP before I get FlexRIO hardware...

I make simple test, but i get little bit strange results...

Labview model and my VHDL code of my component is below...

dram_data_mask_lower <= (others => '0');

dram_data_mask_upper <= (others => '0');

process(aReset, clk) begin

if(aReset = '1') then

dram_write_data_lower <= (others => '0');

dram_write_data_upper <= (others => '0');

data_value_count <= (others => '0');

dram_address <= (others => '0');

dram_command_write_enable <= '0';

dram_command <= (others => '0');

elsif rising_edge(clk) then

if(dram_command_init_done = '1' and dram_command_fifo_full = '0') then

data_value_count <= data_value_count + 1;

dram_write_data_lower(31 downto 0) <= data_value_count;

dram_write_data_lower(63 downto 32) <= data_value_count;

dram_write_data_upper(31 downto 0) <= data_value_count;

dram_write_data_upper(63 downto 32) <= data_value_count;

dram_address(31 downto 2) <= data_value_count(29 downto 0);

dram_command_write_enable <= '1';

dram_command <= "00000000";

else

dram_command_write_enable <= '0';

dram_command <= (others => '0');

end if;

end if;

end process;

DRAM memory simulation model have limit at 2^18 addresses(1MegaByte)...

I wrote sequentially from the address zero until the end of this valid range...

On every 100MHz clock...

But the model always accept the data...

How this is possible?

I fill 256 rows with 1024 columns with data, before simulation finish...

Where is the overhead for the refresh and for precharge row and open the row...

I expect to see sometimes that controller is busy...

How accurate is this short DRAM model of the physical DRAM components?

03-07-2013 08:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Unfortunately, in my experience - the simulation model of the DRAM appears to act like an SRAM (ie: no refresh/charge effects) with a 15-ish clock latency. It does NOT operate that way in hardware, so you should have a buffering scheme on the data inputs and outputs to minimize data-loss.

-J

03-28-2013 10:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a different suggestion, although it isn't really pertinent to your simulation question.

Since you appear to be developing a new application, you should strongly consider using the DRAM Memory Primitive instead of the DRAM CLIP. The simulation of this is still not 100% accurate to hardware latency/etc. However, there are very few use cases where you still must use the DRAM CLIP. The interface on the DRAM Primitive is much cleaner, and much easier to manage buffering schemes.

03-31-2013 07:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Since I am planning to use DRAM memory on the edge of maximum throughput performance...

I managed to make an accurate verilog model using available NI and Xilinx files...

Who is interested can see in attached files...

Thanks to all