- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Question on DMA configuration with multiple FlexRIOs

10-16-2012 10:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey,

Thanks again for all your advice on my last post; it worked like a charm. I now have a somewhat different question that

I was hoping to ask people's advice about.

In the system I'm developing, I have multiple FlexRIO boards that will all be running the same design. The behavior of each board will

be different, based on values written to certain regisers at runtime.

Ideally, I would like to generate one bitfile and push it out to all of the boards. But I have Host to FPGA, FPGA to Host, and Peer-to-Peer

DMA FIFOs in the system. I saw a little documentation on dynamic configuration of these FIFOs, but I'm not sure if that's what I'm after. Right now,

I don't see any way around maintaining multiple vis and hand-editing each vi to reference the proper global FIFO resources for

each corresponding card.

Is there any way to dynamically configure these DMA FIFOs in a way that would let me synthesize a single bitfile?

The best I could think of would be to put all other logic in a reentrant subvi, so that I would only have to separately maintain code

pertaining to the DMAs themselves, but I would still be looking at multiple syntheses, and I'm not sure if there are other

restrictions on resources in reentrant subvi's that I might run into.

I'd be grateful for any suggestions.

- Tags:

- DMA

10-16-2012 11:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It seems like what you're after is the dynamic FPGA references, which would allow you to reuse subVIs for multiple bitifles, as long as each bitfile has the same name for controls/indicators/fifos/etc. All you would have to manage at that point is which reference is wired into each subVI.

Some help documentation is listed here, but I like the FlexRIO Development Tools as an example for the usage of the dynamic reference, just look at the Instrument Drivers (576X, etc.)

10-16-2012 11:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

ZA,

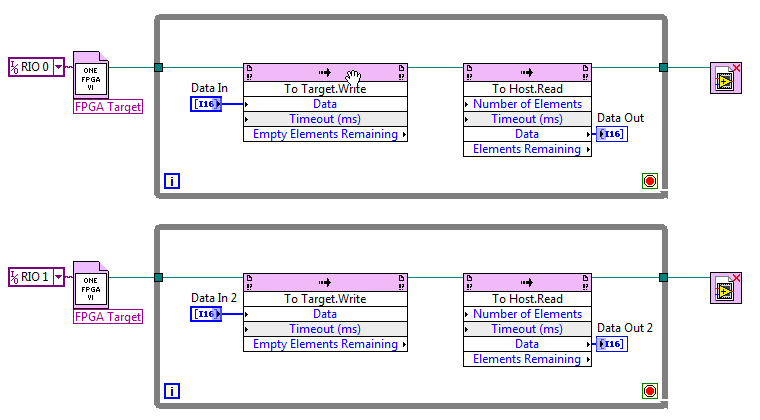

You can certainly generate one bitfile and push it out to all boards, regardless of the naming of your FIFOs. Just create the FPGA bitfile like you would for a single FPGA, then in your Host VI open separate sessions to separate boards, pointing them all to the same bitfile:

In this example, I'm using the same bitfile on two boards. I do this simply by opening two separate sessions and using the proper resource names on the "Open FPGA Reference" VI (RIO 0 and RIO 1). The resulting FPGA VI Reference (the green/teal wire) will uniquely reference the FPGA board you pointed to. In my example above, each of the loops writes/reads only to/from the DMA FIFOs that correspond to their specific NI FlexRIO modules, even though the DMA FIFOs are named the same (because the bitfiles are the same).

This also works if you split up the loops above into separate Host VIs.

10-16-2012 11:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

ZA,

Attached is a 2012 example similar to the above example, but using the dynamic reference, so I just have to create a single subVI and ensure my FPGA VI has named FIFOs.

10-19-2012 02:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, I can now get one bitfile pushed out to all of my boards.