- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Guide to Power Electronics Control Application Examples and IP Cores for NI GPIC

11-12-2015 09:52 PM - edited 01-16-2017 12:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Updated January 2017. Please download the latest library using the link below. See the bottom of this post for details.

This document is a guide to LabVIEW FPGA power electronics control examples and IP.

Dozens of open source example apps. Examples: 3-phase bidirectional active front end (AFE), induction motor VFD (V/Hz, FOC), buck-boost energy storage converter, isolated bidirectional DC (IBDC), …

Hundreds of open source IP cores. Examples: Field oriented control transforms (i.e. ABC to DQ), sine-triangle PWM, space-vector PWM, PID control, 1547 anti-islanding, FRF control stability analyzer, …

LabVIEW 2016 Library

Click here to download the LabVIEW 2016 library. Due to long file paths, you must unzip to a very short path (not desktop) using 7-Zip or WinZip (not default Windows zip utility) and do not install to vi.lib. The path locations below assume you have unzipped the library in a directory named "C:\LabVIEW 2016". The LabVIEW 2016 development toolchain is required (see announcement titled "What tools do I need to get started developing power conversion equipment?"). Examples and IP are provided for both sbRIO-9607 GPIC and sbRIO-9606 GPIC targets when available.

LabVIEW 2015 Library

Click here to download the LabVIEW 2015 library. Due to long file paths, you must unzip to a very short path (not desktop) using 7-Zip or WinZip (not default Windows zip utility) and do not install to vi.lib. The path locations below assume you have unzipped the library in a directory named "C:\LabVIEW 2015". The LabVIEW 2015 development toolchain is required (see announcement titled "What tools do I need to get started developing power conversion equipment?"). Examples and IP are provided for both sbRIO-9607 GPIC and sbRIO-9606 GPIC targets when available.

The attached Code is provided As Is. It has not been tested or validated as a product, for use in a deployed application or system, or for use in hazardous environments. You assume all risks for use of the Code and use of the Code is subject to the Sample Code License Terms which can be found at: http://ni.com/samplecodelicense

Application Examples

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

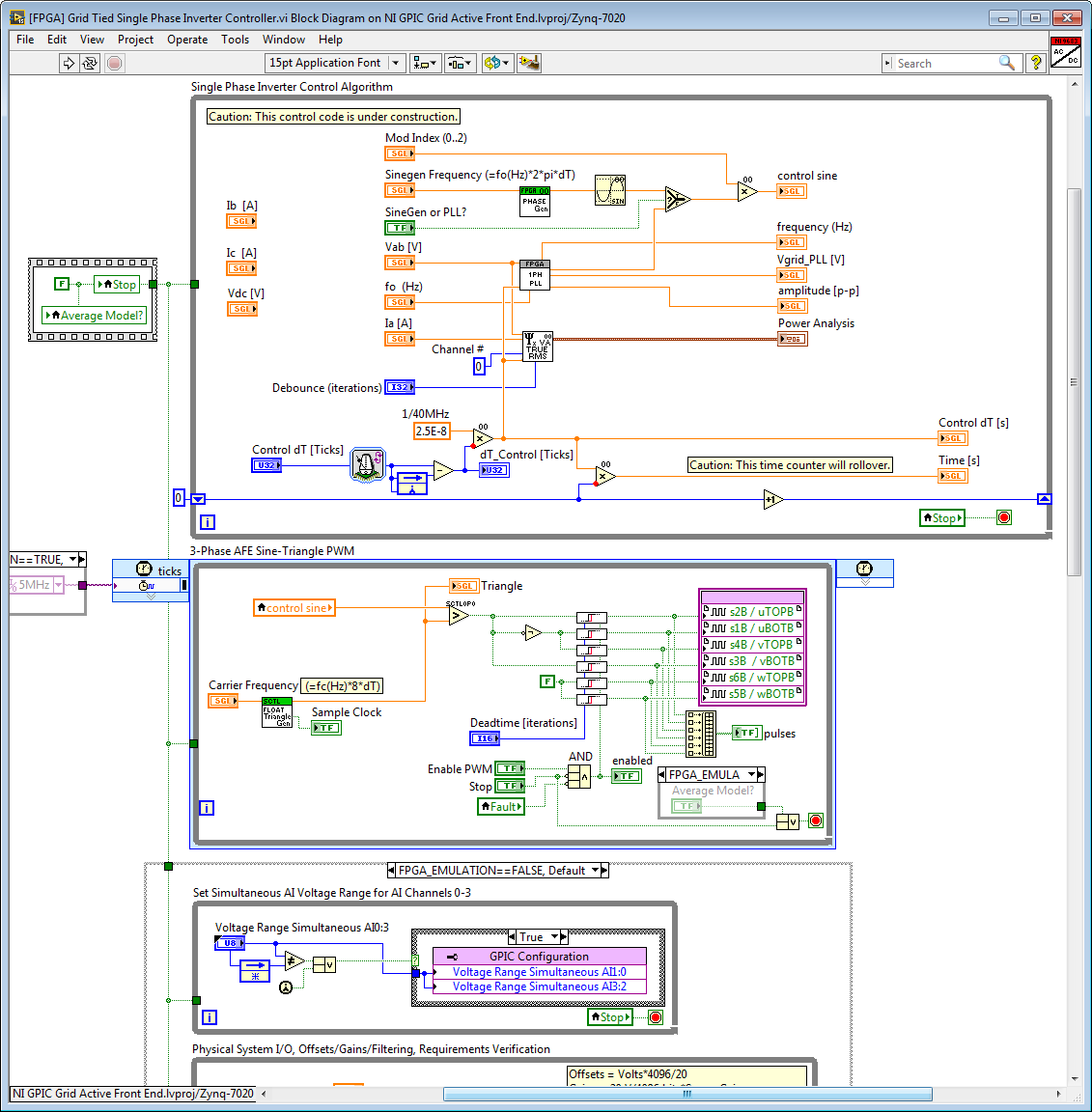

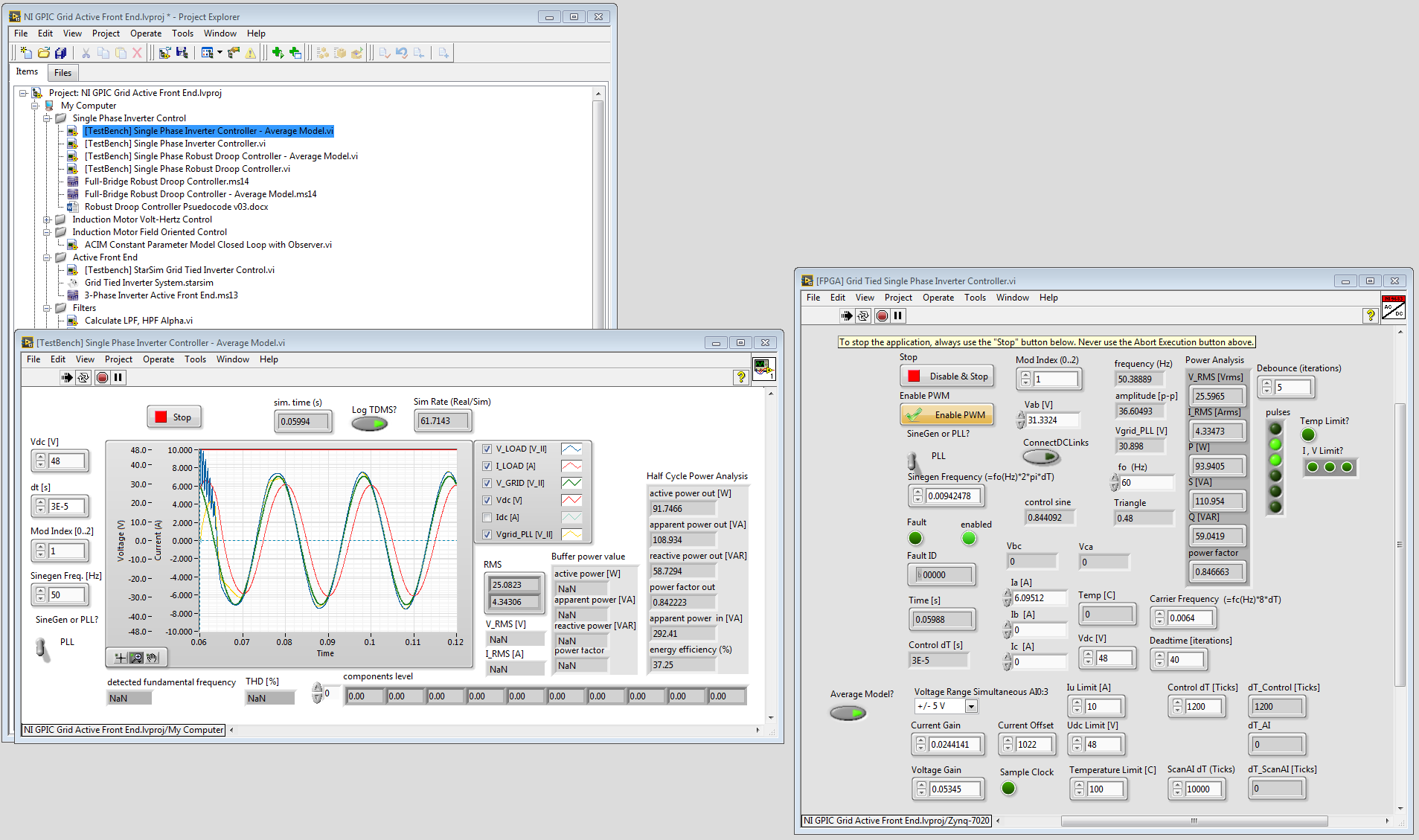

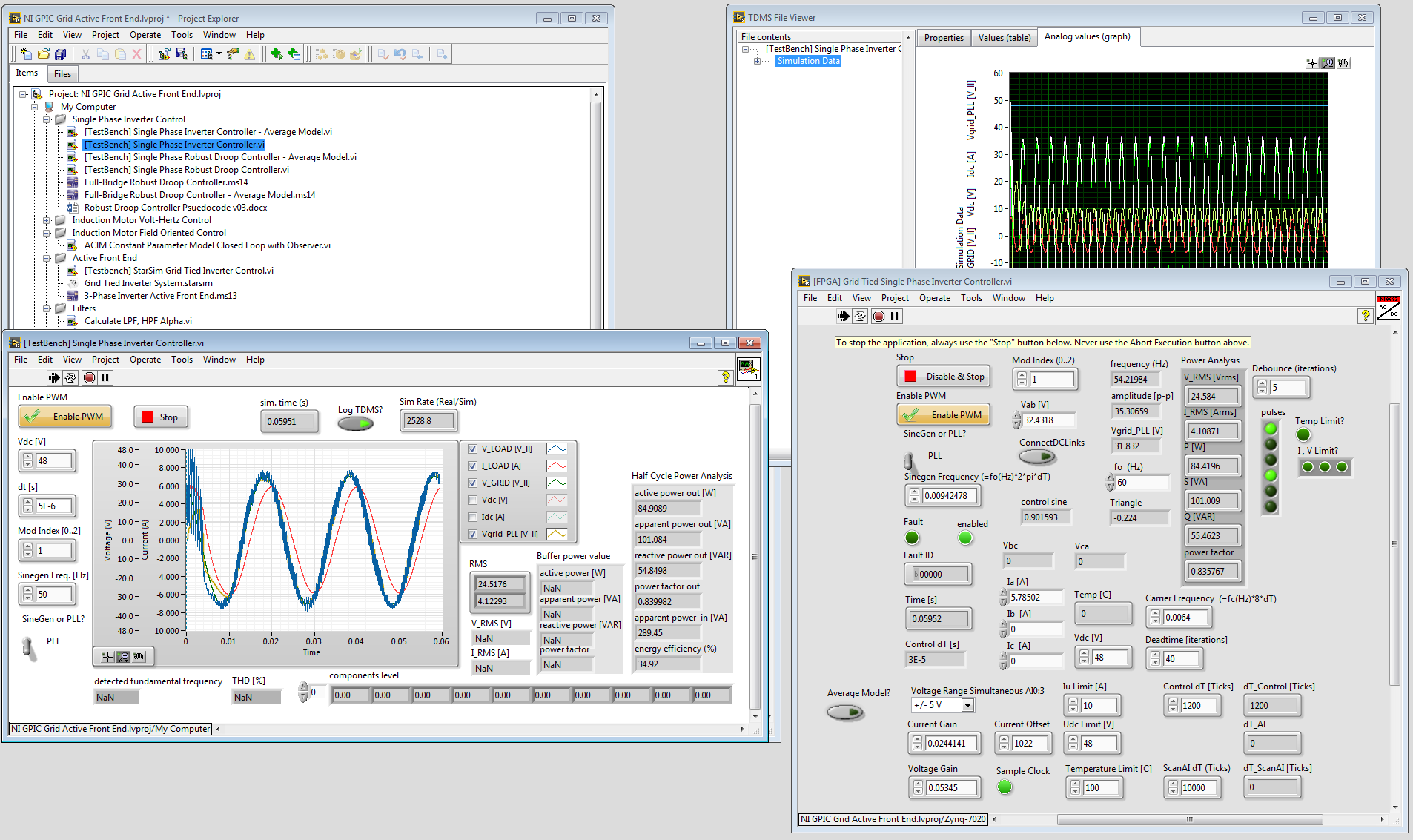

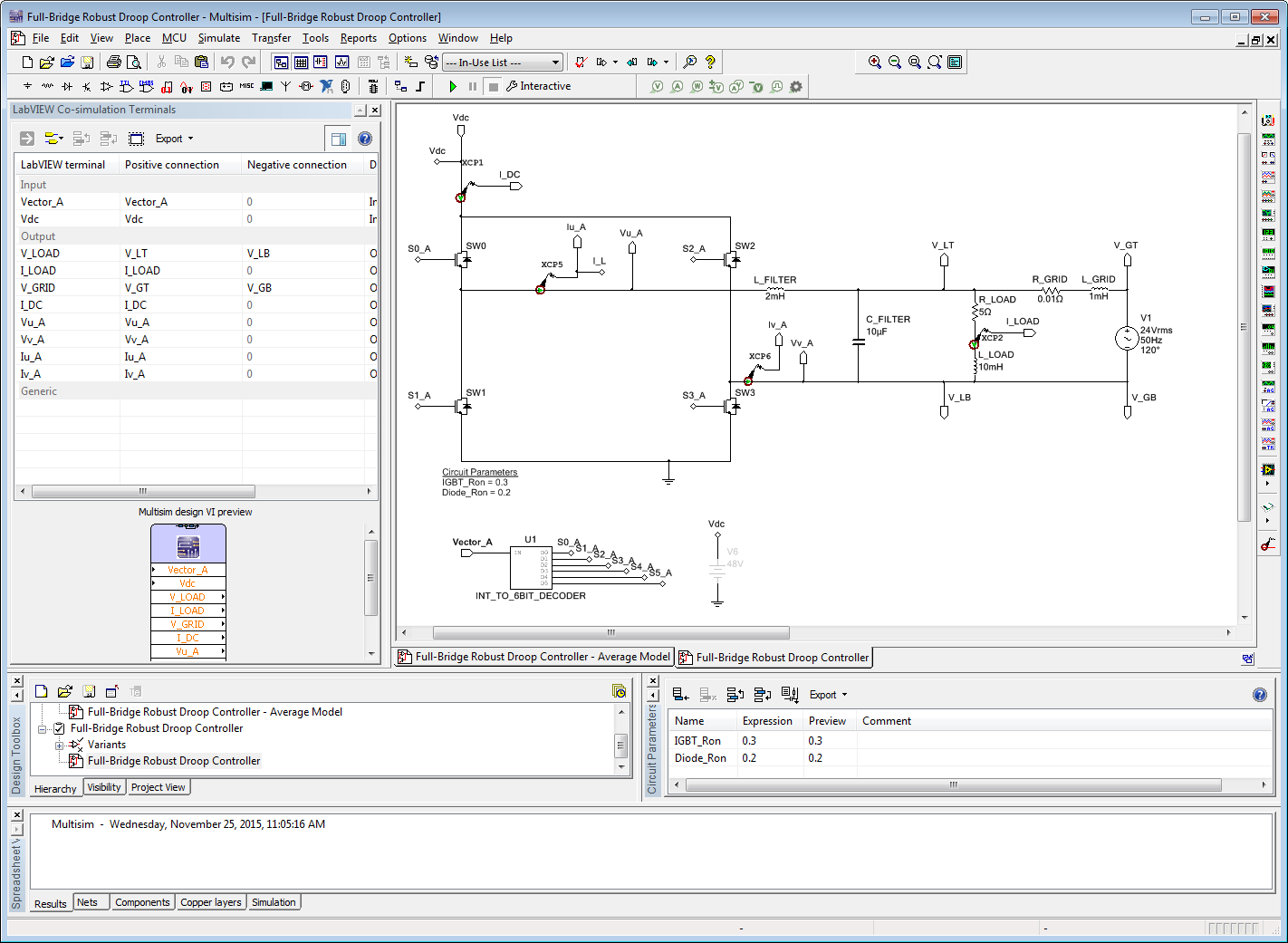

| Single Phase H-Bridge Grid Tied Inverter with Single Phase PLL and True RMS Power Analyzer |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Grid Tied Single Phase Inverter Controller.vi

SMPS Co-Simulation: C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\Testbench\[TestBench] Single Phase Inverter Controller.vi

Average Model Co-Simulation: C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\Testbench\[TestBench] Single Phase Inverter Controller - Average Model.vi |

||

| Open Loop Sine-Triangle PWM Generation, 3-phase |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-AC Inverter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-AC Inverter Control.vi |

||

| DC-to-DC Half-Bridge Converter with Current, Voltage, Speed Cascaded Control |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

, | |

| Grid Tied Inverter Bidirectional Active Front End (AFE) with DC Bus Regulation and 1547 Anti-Islanding | Requires StarSim Offline |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control with FRF Stability Analysis.vi

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control.vi |

|

| Buck-Boost Half-Bridge Bidirectional Energy Storage Converter with Junction Temperature Regulation and Digital Twin |

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\GPIC Half-Bridge Buck-Boost.lvproj

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA 9607] NI GPIC Buck-Boost Energy Storage Converter.vi

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA] NI GPIC Buck-Boost Energy Storage Converter.vi |

||

|

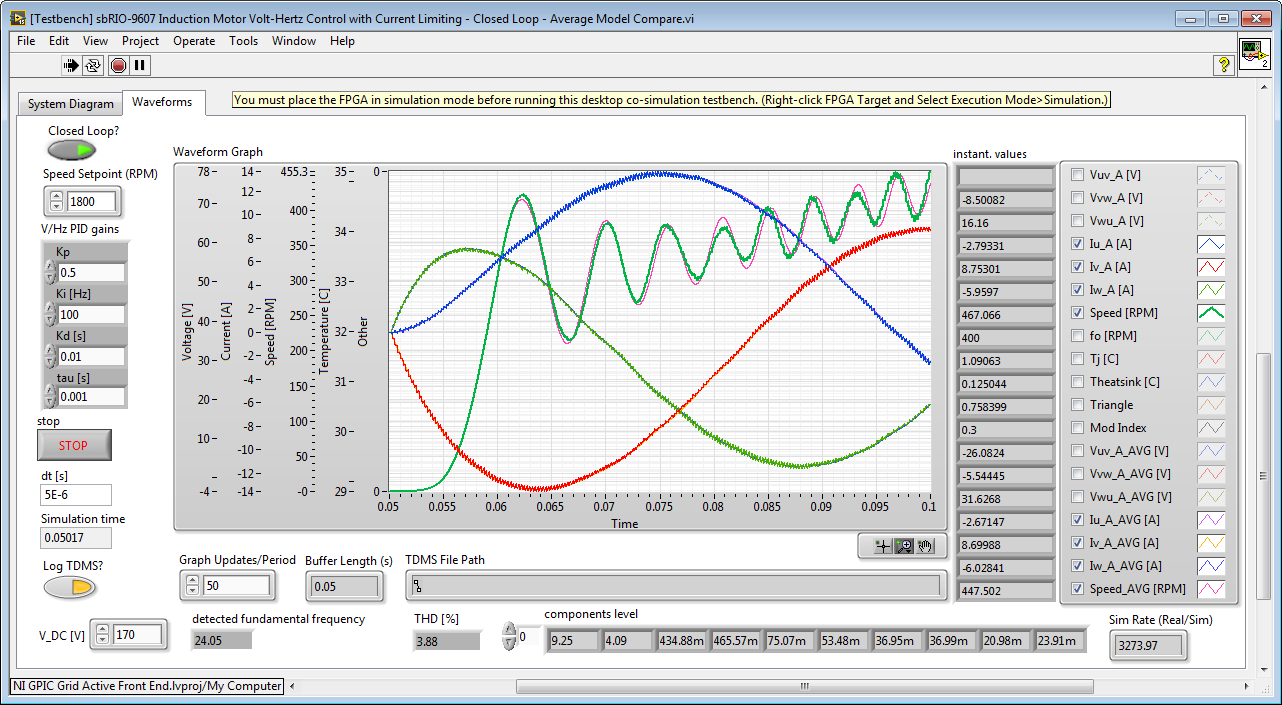

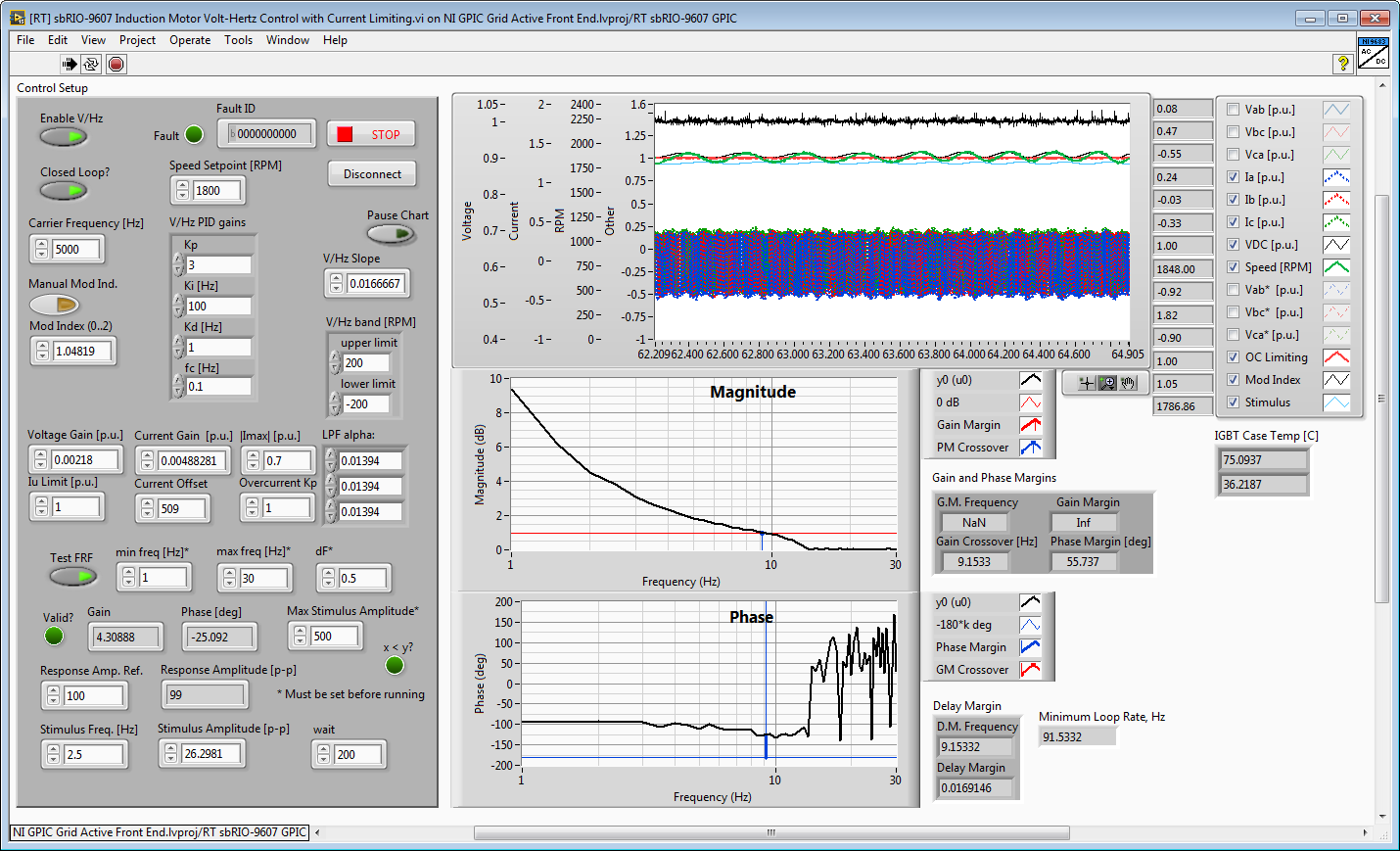

3-Phase Induction Motor Volt/Hertz Control with Current Limiting |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Induction Motor Volt-Hertz Control with Current Limiting.vi |

||

|

3-Phase Induction Motor Field Oriented Control (Vector Control) with Space Vector PWM (SVPWM) |

Requires NI LabVIEW SoftMotion Module |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

In Development (Incomplete): C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Induction Motor FOC NI LabVIEW SoftMotion.vi |

|

| 3-Phase Induction Motor Direct Torque Control (DTC) with Hysteresis PWM (bang-bang) |

C:\LabVIEW 2015\GPIC\GPIC Induction Motor Direct Torque Control (DTC)\NI GPIC Direct Torque Control (DTC).lvproj

C:\LabVIEW 2015\GPIC\GPIC Induction Motor Direct Torque Control (DTC)\SubVIs\[FPGA] DTC flux_torque control float.vi |

||

| In Development: 3-Phase Induction Motor Field Oriented Control with Rotor Flux Observer (Current Model) | Requires NI Electric Motor Simulation Toolkit |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

Code is in the process of being converted from desktop to FPGA implementation. See the desktop average model simulator and FPGA algorithms being ported and tested/validated here:

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\FOC\ACIM Constant Parameter Model Closed Loop with Observer.vi |

Control Loop Examples

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| Sine-Triangle PWM (SPWM) |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Induction Motor Volt-Hertz Control with Current Limiting.vi |

||

| Space Vector PWM (SVPWM) | ftp://ftp.ni.com/evaluation/powerdev/training/SVPWMExample.zip | ||

| Multichannel Low Pass Filter Server |

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\GPIC Half-Bridge Buck-Boost.lvproj

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA 9607] NI GPIC Buck-Boost Energy Storage Converter.vi

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA] NI GPIC Buck-Boost Energy Storage Converter.vi |

||

| Multichannel PID Control Server |

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\GPIC Half-Bridge Buck-Boost.lvproj

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA 9607] NI GPIC Buck-Boost Energy Storage Converter.vi

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA] NI GPIC Buck-Boost Energy Storage Converter.vi |

||

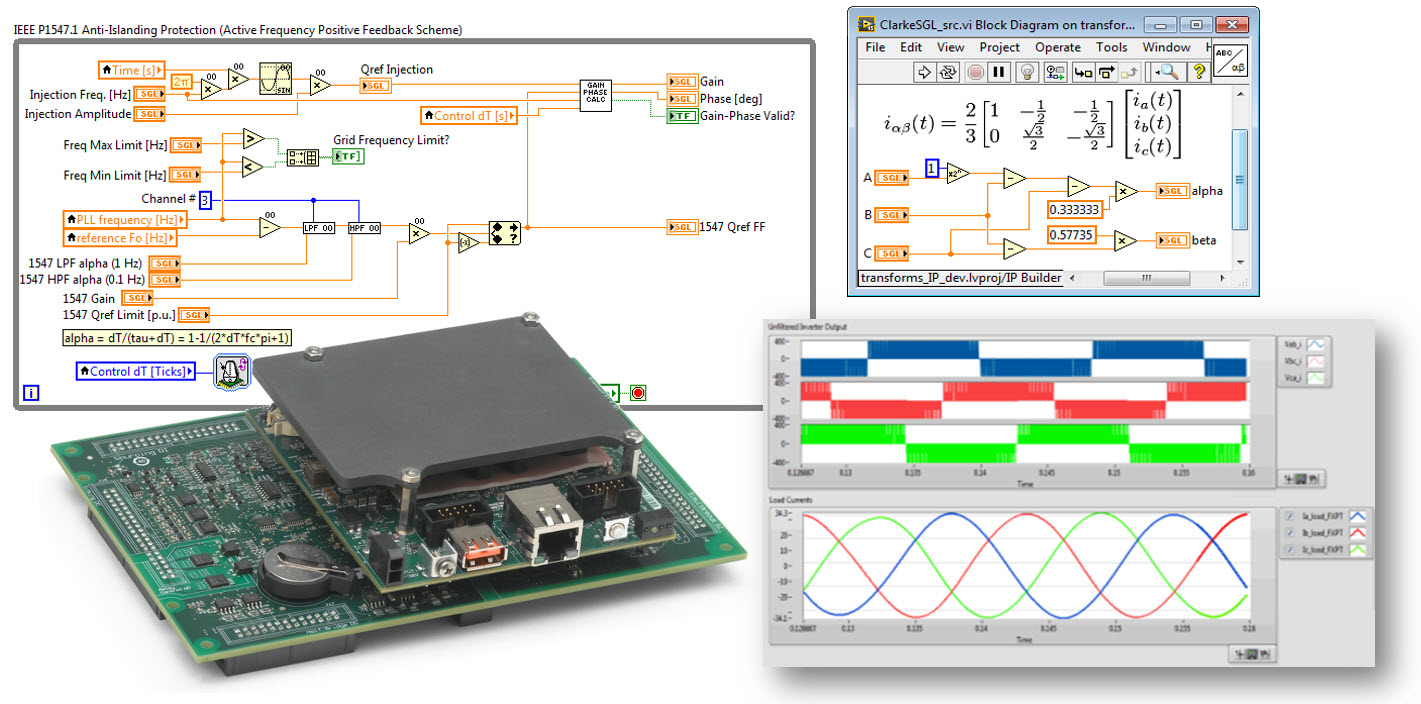

| IEEE P1547.1 Anti-Islanding Protection (Active Frequency Positive Feedback Scheme) |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control with FRF Stability Analysis.vi

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control.vi |

||

| 40 MHz Fault Handling Loop |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Induction Motor Volt-Hertz Control with Current Limiting.vi |

||

| FPGA Control State Machine and RT Watchdog |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| Simultaneous Analog Inputs with Scaling, Filtering and Range Checking |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| IGBT Thermistor Temperature Scaling and Range Checking |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| Control loop gain FRF stability analyzer |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\NI GPIC Grid Active Front End.lvproj

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Induction Motor Volt-Hertz Control with Current Limiting.vi |

||

| Precharge Contactor Management |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| Quadrature Encoder Interface |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| Write Offsets, Gains and Limits to FPGA RAM |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

||

| SKiiP3 Power Stack Error Signal Monitoring |

C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] sbRIO-9607 GPIC 3-Phase DC-to-DC Converter Control.vi

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC 3-Phase DC-to-DC Converter Control.vi |

IP Cores: Control

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| Rotor Flux Observer (Current Model) |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] Float Rotor Flux Observer - Current Model.vi

Code is in the process of being converted from desktop to FPGA implementation. See the desktop average model simulator and FPGA algorithms being ported and tested/validated here:

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\FOC\ACIM Constant Parameter Model Closed Loop with Observer.vi |

||

| [FPGA] Rising Edge Delay with Enable (Deadtime Insertion).vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] Rising Edge Delay with Enable (Deadtime Insertion).vi | ||

| 3-Phase PLL | Palette: FPGA Math & Analysis>Control>3-Phase PLL | ||

| [FPGA] Single-Phase PLL with Frequency and Amplitude (FLOAT).vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Single-Phase PLL with Frequency and Amplitude (FLOAT).vi | ||

| [FPGA] Float TriangleGen (use inside SCTL).vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] Float TriangleGen (use inside SCTL).vi | ||

| [FPGA] Float PhaseGen Basic 00.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] Float PhaseGen Basic 00.vi | ||

| Multichannel PID | Palette: FPGA Math & Analysis>Control>PID | ||

| [FPGA] Quadrature Encoder dX Method.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Sensor IF\[FPGA] Quadrature Encoder dX Method.vi | ||

| Space Vector Modulation |

Requires NI LabVIEW SoftMotion Module |

C:\Program Files (x86)\National Instruments\LabVIEW 2015\vi.lib\Motion\MotorControl\_s\nism.svm.fxp.vi | |

| Space Vector Modulation | ftp://ftp.ni.com/evaluation/powerdev/training/SVPWMExample.zip | ||

| Hysteresis PWM (bang-bang) | Discussion thread | ftp://ftp.ni.com/evaluation/powerdev/training/MaglevHysteresis2014.zip | |

| [FPGA] GPIC RAW AI - Scale and Low Pass Filter.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Sensor IF\[FPGA] GPIC RAW AI - Scale and Low Pass Filter.vi | ||

| [FPGA] GPIC Write & Read FPGA RAM Constants.vi | C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC Write & Read FPGA RAM Constants.vi | ||

| [FPGA] RIO Elapsed Time Watchdog.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] RIO Elapsed Time Watchdog.vi | ||

| [FPGA] Time Since Edge (40 MHz).vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Basic\[FPGA] Time Since Edge (40 MHz).vi | ||

| [FPGA] StarSim Three-Phase Active and Reactive Power.vi |

Requires StarSim Offline |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\IP Cores - LabVIEW FPGA\StarSim\[FPGA] StarSim Three-Phase Active and Reactive Power.vi | |

| [FPGA] StarSim_3PPLL_sub(lineV).vi |

Requires StarSim Offline |

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\IP Cores - LabVIEW FPGA\StarSim\[FPGA] StarSim_3PPLL_sub(lineV).vi | |

|

ABC to DQ |

Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\ABCtoDQSGL_gen.vi | |

|

DQ to ABC |

Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\DQtoABCSGL_gen.vi | |

|

ABC to alpha, beta (Clarke Transform) |

Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\ClarkeSGL_gen.vi | |

|

alpha, beta to ABC (Inverse Clarke Transform) |

Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\InvClarkeSGL_gen.vi | |

|

alpha, beta to DQ (Park Transform) |

Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\ParkSGL_gen.vi | |

| DQ to alpha, beta (Inverse Park Transform) | Discussion thread | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Transforms\IPBuilder\Generated\InvParkSGL_gen.vi | |

| Multichannel Transfer Function Solver (Performance Optimized) |

C:\LabVIEW 2015\HIL Simulation\Transfer Function Solver\FPGA Transfer Function HIL Solver.lvproj

C:\LabVIEW 2015\HIL Simulation\Transfer Function Solver\subVIs\[FPGA] cRIO-9082 FPGA Transfer Function Simulator v01.vi |

||

| Multichannel Transfer Function Solver (Resource Optimized) |

C:\LabVIEW 2015\HIL Simulation\Transfer Function Solver\FPGA Transfer Function HIL Solver.lvproj

C:\LabVIEW 2015\HIL Simulation\Transfer Function Solver\subVIs\[FPGA] cRIO-9082 FPGA Transfer Function Simulator (RESOURCE OPTIMIZED) v01.vi |

||

| Multichannel State Space Solver (Performance Optimized) |

C:\LabVIEW 2015\HIL Simulation\State-Space Solver\FPGA State-Space HIL Solver.lvproj

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\HIL Solver\[FPGA] Floating-Point State-Space Solver.vi |

||

| Multichannel State Space Solver (Resource Optimized) |

C:\LabVIEW 2015\HIL Simulation\State-Space Solver\FPGA State-Space HIL Solver.lvproj

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\HIL Solver\[FPGA] Floating-Point State-Space Solver (RESOURCE OPTIMIZED) 00.vi |

||

| Buck-Boost Energy Storage Converter Circuit FPGA RT Simulator with Junction Temperature, Switching and Conduction Loss |

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\GPIC Half-Bridge Buck-Boost.lvproj

C:\LabVIEW 2015\GPIC\GPIC Half-Bridge Buck-Boost\Sensorless Maglev\FPGA\[FPGA] NI GPIC Buck-Boost Energy Storage Converter.vi |

IP Cores: Digital Signal Processing and Analysis

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| FPGA] True RMS Power Quality Analyzer Multichannel |

Vrms Irms P S [VA] Q [VAR] power factor

Note: I, V signals must cross zero. Need to add code to remove DC offset. |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] True RMS Power Quality Analyzer Multichannel 00.vi

Example: C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Grid Tied Single Phase Inverter Controller.vi |

|

| [FPGA] Zero Crossing with Debounce Float.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Zero Crossing with Debounce Float.vi | ||

| [FPGA] First Order Low Pass Filter Multichannel with Alpha terminal (FLOAT) 00.vi |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] First Order Low Pass Filter Multichannel with Alpha terminal (FLOAT) 00.vi

Utility [Desktop]: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Testbench\Calculate LPF, HPF Alpha.vi

Example [Desktop]: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Example\Multichannel FPGA Low Pass Filter Example.vi

Testbench [Desktop]: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Testbench\Test [FPGA] Low Pass Filter.vi |

||

| [FPGA] First Order High Pass Filter Multichannel with Alpha terminal (FLOAT) 00.vi |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] First Order High Pass Filter Multichannel with Alpha terminal (FLOAT) 00.vi

Utility [Desktop]: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Testbench\Calculate LPF, HPF Alpha.vi

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Testbench\Test [FPGA] High Pass Filter.vi |

||

| Half/Full Cycle RMS | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] DC and RMS Measurements - Update on Zero Crossing.vi | ||

| [FPGA] Rise Time & Steady State Error Calc Float 00.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Rise Time & Steady State Error Calc Float 00.vi | ||

| [FPGA] Max, Min, Delta Float.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Max, Min, Delta Float.vi | ||

| [FPGA] Gain and Phase Calculation Float.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] Gain and Phase Calculation Float.vi | ||

| Quantizer Float.vi |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Quantizer Float.vi

Testbench [Desktop]: C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\Testbench\Test FPGA Quantizer.vi |

IP Cores: System Identification and Signal Generation

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| [FPGA] PRBS Generator Binary PtByPt.vi |

C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] PRBS Generator Binary PtByPt.vi

Example: C:\LabVIEW 2015\GPIC\GPIC Reference Design\GPIC Reference Design LabVIEW 2015.lvproj

C:\LabVIEW 2015\GPIC\GPIC Reference Design\FPGA\[FPGA] GPIC PRBS Converter Control.vi |

||

| White Noise | Palette: FPGA Math & Analysis>Generation>White Noise |

IP Cores: Utilities

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| One Shot U32.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Basic\One Shot U32.vi | ||

| Interval Counter U32.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Basic\Interval Counter U32.vi | ||

| [FPGA] Time Since Edge (40 MHz).vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Basic\[FPGA] Time Since Edge (40 MHz).vi | ||

| [FPGA] RIO Multi-Channel Debounce Filter.vi | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] RIO Multi-Channel Debounce Filter.vi |

IP Cores: Floating Point Math for Use Outside Single-Cycle Timed Loop (Optimized for Resource Sharing)

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| Add 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Add Float.vi | |

| Subtract 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Subtract Float.vi | |

| Multiply 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Multiply Float.vi | |

| Divide 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Divide Float.vi | |

| Increment 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Increment Float.vi | |

| Decrement 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Decrement Float.vi | |

| Absolute Value 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Absolute Value Float.vi | |

| Scale By Power Of 2 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Scale By Power Of 2 Float.vi | |

| Square Root 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Root Float.vi | |

| Square 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Float.vi | |

| Negate 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Negate Float.vi | |

| Reciprocal 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Reciprocal Float.vi | |

| Sign 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Sign Float.vi | |

| Sine LUT 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Sine Float.vi | |

| Cosine LUT 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Cosine Float.vi | |

| Sine & Cosine CORDIC 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Sine & Cosine CORDIC Float.vi | |

| Exponential LUT 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Exponential LUT Float.vi | |

| Natural Logarithm 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Natural Logarithm Float.vi | |

| Power of X 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Power of X Float.vi | |

| Quantizer 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Quantizer Float.vi | |

| Equal Float 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Equal Float.vi | |

| Not Equal 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Not Equal Float.vi | |

| Less Than 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than Float.vi | |

| Less Than or Equal 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than or Equal Float.vi | |

| Greater Than 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than Float.vi | |

| Greater Than or Equal 00..04 | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than or Equal Float.vi |

IP Cores: Floating Point Math for Use Inside Single-Cycle Timed Loop (Optimized for Performance)

| Description |

Features |

Location |

Screenshot |

|---|---|---|---|

| Add Float SCTL 40 MHz Latency 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Add Float SCTL 40 MHz Latency 1.vi | |

| Add Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Add Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Add Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Add Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Subtract Float SCTL 40 MHz Latency 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Subtract Float SCTL 40 MHz Latency 1.vi | |

| Subtract Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Subtract Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Subtract Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Subtract Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Multiply Float SCTL 40 MHz Latency 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Multiply Float SCTL 40 MHz Latency 1.vi | |

| Multiply Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Multiply Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Multiply Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Multiply Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Divide Float SCTL 40 MHz Latency 5.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Divide Float SCTL 40 MHz Latency 5.vi | |

| Multiply Add Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 Only).vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Multiply Add Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 Only).vi | |

| Square Root Float SCTL 40 MHz Latency 5 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Root Float SCTL 40 MHz Latency 5 Pipeline 0.vi | |

| Square Float SCTL 40 MHz Latency 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Float SCTL 40 MHz Latency 1.vi | |

| Square Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Square Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Square Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Reciprocal Float SCTL 40 MHz Latency 5 (Zynq and Kintex-7 Only).vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Reciprocal Float SCTL 40 MHz Latency 5 (Zynq and Kintex-7 Only).vi | |

| Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Not Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Not Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Not Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Not Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Greater Than Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Greater Than Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Less Than Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Less Than Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Greater Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Greater Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Greater Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Less Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 1.vi | |

| Less Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Less Than or Equal Float SCTL 40 MHz Latency 0 Pipeline 0.vi | |

| Exponential Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 only).vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Exponential Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 only).vi | |

| Natural Logarithm Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 only).vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Natural Logarithm Float SCTL 40 MHz Latency 2 (Zynq and Kintex-7 only).vi | |

| Sine & Cosine CORDIC SCTL 40 MHz Latency 16.vi | White Paper | C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Sine & Cosine CORDIC SCTL 40 MHz Latency 16.vi |

March 16, 2016 Update

The master library of examples and IP has just been updated. The download link is the same. The old version is archived here.

The new version includes:

- FPGA Proportional Resonant with Phase Compensation and Harmonic Elimination (C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Grid Tied Single Phase Inverter Controller with Harmonic Compensation v06.vi)

- FPGA Harmonic Level Detection and Harmonic Waveform Extraction (C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\SubVIs\[FPGA] Grid Tied Single Phase Inverter Controller with Harmonic Compensation v06.vi)

- FPGA Three-Phase True RMS Power Analysis with Line-to-Line to Line-to-Neutral Converter (C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Grid Tied AFE Control with FRF Stability Analysis.vi)

- FPGA Small Signal Injection for Control Loop Gain Margin and Phase Margin Stability Analysis (C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[FPGA] Induction Motor Volt-Hertz Control with Current Limiting.vi)

- Discrete Integrator Backward Euler and Trapezoidal Methods for IP Builder (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\HIL Solver\[FPGA] DiscreteIntegrator Trapezoidal Multichannel IP Builder.vi)

- FPGA LR filter transfer function observer (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Analysis\[FPGA] LR Filter (FLOAT) 01.vi), new FPGA Timekeeper code for digitally phase locked control systems (C:\LabVIEW 2015\TimeKeeper)

- FPGA Transmission Line Delay Simulator (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Floating Point\Variable Depth FIFO.vi)

- FPGA Inverse Notch Filter (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Control & Signal Gen\[FPGA] Inverse Notch Filter Multichannel - dt = 50 us (2000 Ticks) 04.vi)

- FPGA Thermocouple Scaling (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Sensor IF\[FPGA] K Thermocouple Scaling.vi)

- FPGA Integer Divider Remainder/Fraction functions for 64 bit integers (C:\LabVIEW 2015\IP Cores\IP Cores - LabVIEW FPGA\Math)

We hope you will help us test and improve the new IP cores and examples, and their documentation.

Note that the Real-Time processor portion of the GPIC Reference Design Code for sbRIO-9607 GPIC is currently under development.

Note: Under construction. To be continued. This document will be updated frequently...

11-17-2015 01:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi BMac,

can you please suggest the best way to simulate a single phase pwm inverter using labview and multisim such that the control signal is built in fpga which can be used for NI-GPIC.

Also, please suggest the best way to generate a sine pwm output upto 40kHz frequency from NI-GPIC.

Best regards,

T@rminat0r

11-18-2015 09:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Where can I get the NI Circuit Design Suite Application Softwar(for LabVIEW 2015)?

The current version of "NI Circuit Design Suite" is 14.0(for LabVIEW 2014).

The power electronics control application examples can not run.

11-19-2015 10:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

1. First, be sure you have installed the LabVIEW Control Design and Simulation Module 2015 for LabVIEW 2015.

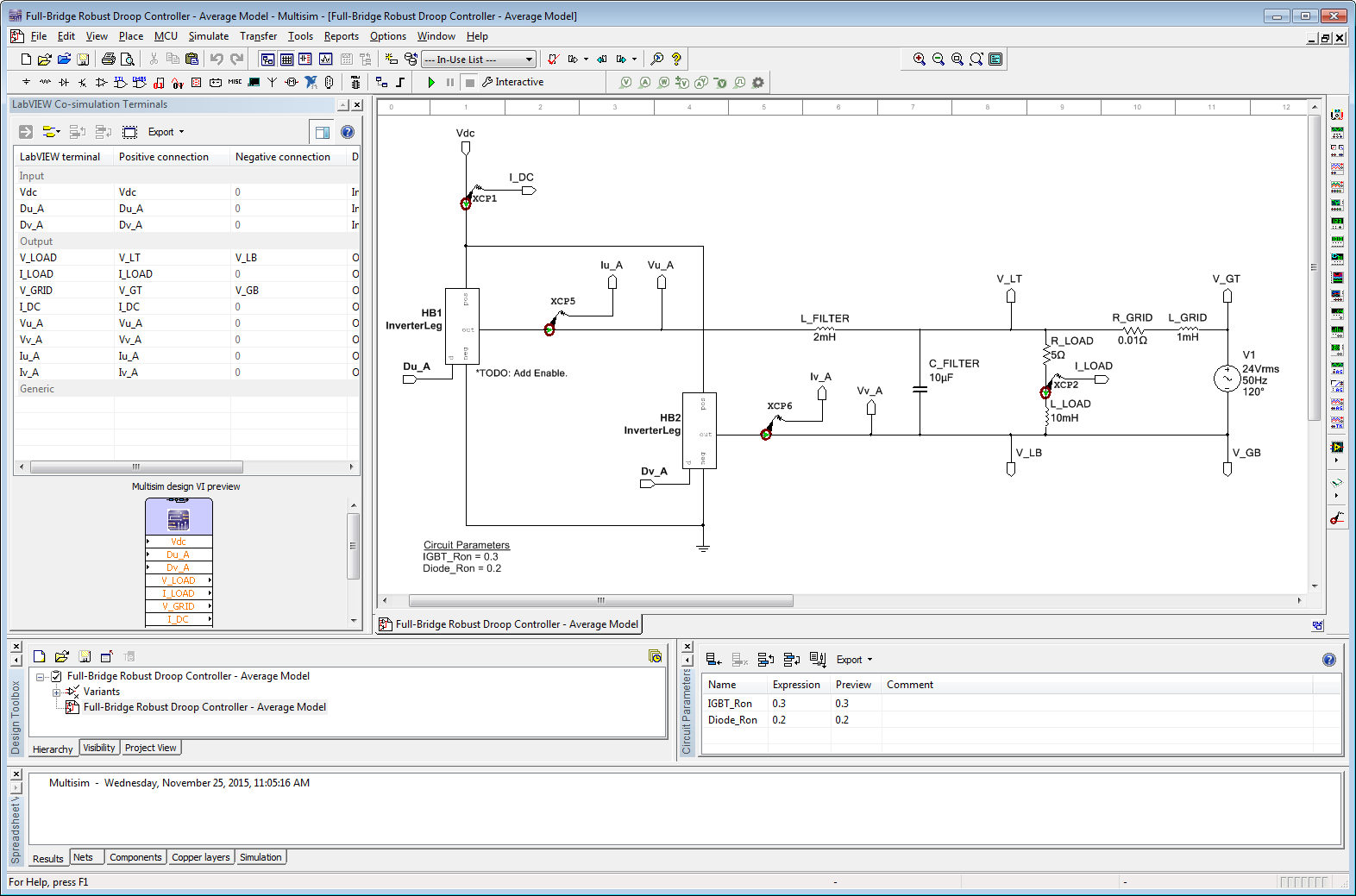

2. Next, click here to download NI Circuit Design Suite 14.0 Full or Pro (Multisim/Ultiboard). Run the installer again and select the option to install the co-simulation plug-in for LabVIEW 2014. You do not need to have LabVIEW 2014 installed. Then follow the instructions below to move the plug-ins to LabVIEW 2015 directories.

3. IMPORTANT: Co-simulation is available and supported for LabVIEW 2015 and Multisim 14 but requires some special steps to enable it. Be sure to install the LabVIEW Control Design and Simulation Module 2015 for LabVIEW 2015. When you install Multisim 14, be sure to install the co-simulation plug-in for LabVIEW 2014. You do not need to have LabVIEW 2014 installed. Then copy the folders and files to the equivalent LabVIEW 2015 directory locations as explained below.

The trick is that, after installing the co-simulation plug in, you need to copy the folders and files below from the LabVIEW 2014 directory to the equivalent LabVIEW 2015 directory:

C:\Program Files\National Instruments\LabVIEW 2014\vi.lib\Simulation\EMI\Plugins\Multisim Design

C:\Program Files\National Instruments\LabVIEW 2014\help\msmcosim.chm

C:\Program Files\National Instruments\LabVIEW 2014\help\msmcosim.txt

IMPORTANT NOTE:

- You must keep your Multisim files and LabVIEW co-simulation VI files in the same directory path. For co-simulation with Multisim 14, the Multisim circuit design files must be located in the same directory path as the LabVIEW co-simulation VI. Otherwise a crash will occur if the Multisim file path is changed. This is a known issue that will be fixed in the future. In the mean time, the workaround is straightforward: You must keep your Multisim files and LabVIEW co-simulation VI files in the same directory path.

11-25-2015 11:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Regarding single-phase inverter simulation and control, I've added an example application to the library for you. Please see the entry above under Application Examples titled "Single Phase H-Bridge Grid Tied Inverter with Single Phase PLL and True RMS Power Analyzer". This provides an example for the single-phase PLL to lock to the grid with sine triangle PWM.

This new example also shows off two really cool new capabilities:

1. A True RMS Power Analyzer IP core for LabVIEW FPGA that calculates active power, apparent power, reactive power, power factor, voltage RMS, and current RMS values.

2. An average model for IGBT half-bridges that simulates up to 700 times faster in co-simulation with LabVIEW FPGA than the switched mode power supply (SMPS) models. The average model includes IGBT and Diode on resistances but neglects forward voltage drop (which are typically negligibly small compared to the DC link voltage). The average model simulates the current draw on the DC Link voltage so it can be used for modeling back-to-back converters. On thing it is missing at present is a way to simulate a disabled inverter (IGBTs always off). Average models are very useful for control algorithm design, tuning and stability analysis.

Here is a screenshot of the FPGA control application. It also supports open loop (non phased locked) sine-triangle PWM generation.

Here are screenshots of co-simulating with the Multisim average model. Note that it's running just 61.7 times slower than real-time. Also note the power analysis on the front panel of the FPGA VI, which matches the independent calculations on the desktop co-simulation testbench application.

Here are screenshots of the switched mode (SMPS) simulation. Note that the switched mode simulation is running 2528.8 times slower than real-time. The TDMS log file viewer from the average model simulation run is shown in the background.

Note that the single-phase inverter control application does not include power factor correction. We could enable this by adding single phase AB(C) to DQ transform and DQ to ABC transform IP cores (see page 31 here http://www.nrel.gov/docs/fy06osti/38017.pdf). Let me know if you'd like to workshop this together as a community project.

Please treat the Multisim half-bridge average models as "under construction" and let us know your feedback. To see an example for a three-phase inverter and induction machine and a comparison between the SMPS and Average model results, open this testbench:

C:\LabVIEW 2015\GPIC\GPIC Grid Active Front End\[Testbench] sbRIO-9607 Induction Motor Volt-Hertz Control with Current Limiting - Closed Loop - Average Model Compare.vi

Note that the switching and average model current waveforms are right on top of each other. The THD is calculated using the switching model.

Note that the average model only testbench shows how to measure the loop gain stability by opening the control loop and injecting a small signal sinewave, and calculating the Bode Plots and analyzing stability (gain and phase margins). The RT application for induction motor V/Hz control performs the same analysis on the actual/physical three-phase inverter and induction machine.

Here is a screenshot of the loop gain frequency response function analysis run on the actual 3-phase inverter with induction motor. I used the analyzer to professionally tune the PIFD control algorithm for the desired gain and phase margins (9 dB, 55 degrees). This is using the new floating point PID algorithm for LabVIEW FPGA (standard function on the palette). I'm using the derivative filter to effectively enable pole placement and enhanced stability. It's very exciting to be able to do this on an actual running inverter!

Please also treat the FPGA gain/phase calculator as under construction and let us know your feedback.

02-09-2016 03:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi BMac,

I was wondering if there was a power electronics ip library for LabView 2014. I've been doing some development in 2014 and would like to forego an install. Thanks for the insight above.

02-11-2016 03:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, a lot of the examples and IP listed above are available for LabVIEW 2014, although they are slightly older versions in some cases of course. I've gone completely to LabVIEW 2015 because it's required for the new sbRIO-9607 Zynq-7020 General Purpose Inverter Controller since it runs open source RT Linux on the ARM microprocessors (rather than VxWorks on the PowerPC of the sbRIO-9606 GPIC) and uses the Xilinx Vivado compiler for the DSP cores and FPGA fabric (rather than Xilinx ISE for the Spartan-6 FPGA of the sbRIO-9606 GPIC).

Here are links to LabVIEW 2014 versions where available:

StarSim Grid Tied Active Front End 2014 (also see the the StarSim Power Electronics Control IP Toolkit for LabVIEW FPGA)

Space Vector PWM IP Builder Example 2014

Maglev Hysteresis PWM Controller 2014

Floating Point Toolkit and Solvers including Real-Time Power Converter HIL Simulation

When you are ready to upgrade to LabVIEW 2015 you can find download links and instructions in the announcement at the ni.com/powerdev site titled "What tools do I need to get started developing power conversion equipment?" Here's a link:

Announcement: What tools do I need to get started developing power conversion equipment?

02-13-2016 06:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

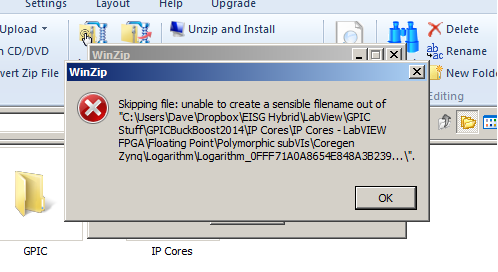

I just unzipped Buck Boost Controller Zip file and I recieved this error for at least 10 files, after that I recieved a different error for up to 3o files where the error had to do with a missing path.

02-14-2016 08:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You must unzip in a very short path such as C:\LabVIEW 2014 using 7-Zip or WinZip, not the native windows zip utility.

02-25-2016 12:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I noticed that we are missing the "quotient and remainder" function for floating point math on FPGA. I have come across a situation where I could use this to keep the angle estimate between +/- pi.