- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How fast is my NI-9205 sampling?

01-12-2018 05:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

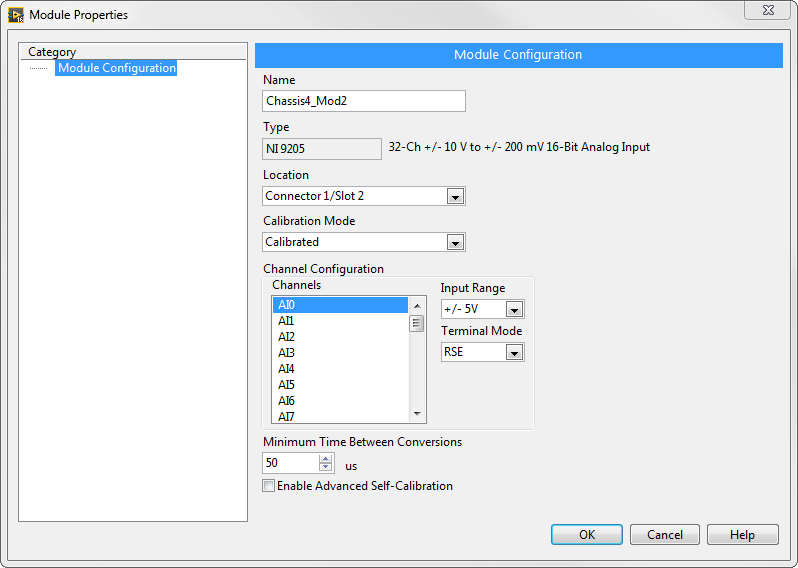

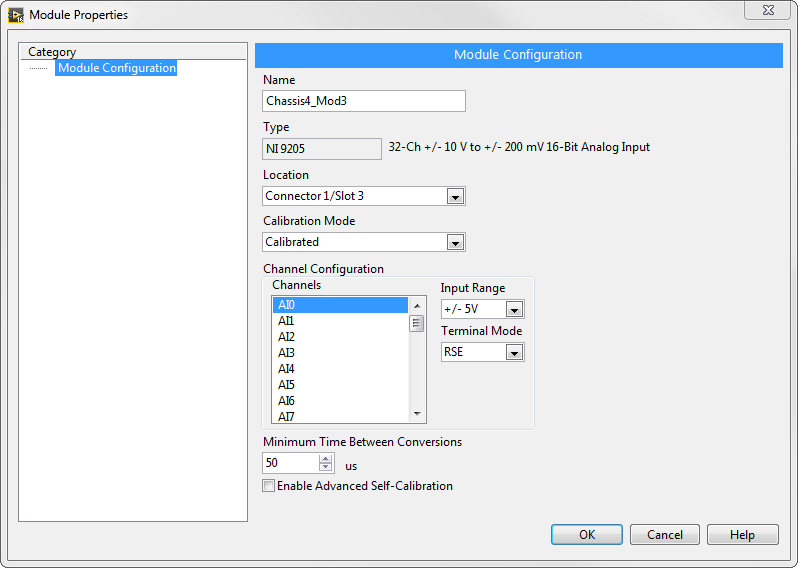

I've got a NI-9205 hooked up to a PXI-7813R via an expansion chassis and configured as follows. The spec says that in this case, the fastest "conversion time" is 4.5us (222Ks/s). Is this per channel, and must all 32 channels be sampled in sequence? According to the NI 9205 FPGA driver interface for the FPGA I/O Node, there is no adjustment on number of channels, so it seems all 32 must be sampled. So, the actual fastest sample rate is 222KS/s / 32 = 6.94KS/s. Can someone please confirm this for sure? I saw these two conflicting articles 1 and 2 and am onfused. Now, I'm trying analyze existing FPGA code that configures the 9205 as follows. Does this mean that my sample rate is actually 50us (20KS/s) / 32 = 625S/s? Can somebody please confirm? Thank you!

01-12-2018 06:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The spec reads as if that is the conversion time for the ADC. So that would mean you have to divide the 222kS/s by the number of channels you are sampling. It should not have to go through all of the channels if you are only using a subset.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

01-17-2018 01:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you. Wondering how the 9205 knows the number of channels the FPGA code is sampling. Does it find out from the FPGA I/O Node? Is any of this documented anywhere?

01-17-2018 02:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@andy_3141593 wrote:

Wondering how the 9205 knows the number of channels the FPGA code is sampling. Does it find out from the FPGA I/O Node?

The compiler sees everything in your code. It can easily figure out which channels you are using.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

01-17-2018 02:44 PM - edited 01-17-2018 02:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

FYI, I'm pretty sure it would be equivalent to put the feedback node after the build array.

The backend of the FPGA IO node probably iterates through each row on the node generating code for each. The code for the second channel runs after the code for the first channel finishes and so forth. And there's of course some intelligent pipelining to make that efficient since it's all in the same block.

You could benchmark your code with something like this:

http://www.ni.com/example/30439/en/

Then you'd know your sample rate for sure.

01-17-2018 03:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks! Now, the properties window for the project entry for the 9205 is as follows. Does the 50us "Minimum time between samples" slow down the 9205 sampling from 4.5us down to 50ms?

01-17-2018 03:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry, from 4.5us to 50us?

01-17-2018 03:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I believe so but I would definitely try it out to see if there's some extra time in the background communicating to the ADC. That is, you might get something like 51us per sample instead of the expected 50us.