- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 9401: output freeze

Solved!04-12-2023 12:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am currently working on a motor control which runs on the FPGA of a cRIO-9082. The software computes six PWM signals (Figure1) which are used to switch the IGBTs of an inverter. These signals are output via a NI-9401 DIO module.

Everything is working so far, however, the DIO module occasionally freezes. When this happens, the output voltages do not change for many milliseconds (Figure2). After that, the module is working normally again (Figure3). These freezes occur randomly – sometimes after only one minute, sometimes after 15 minutes.

I am pretty sure the problem is not with the software, since I have also programmed a VI that would prevent such errors by monitoring the on/off period of each signal. Signal computation and output via a FPGA I/O node is done inside a single-cycle timed loop.

The PWM frequency is set to 10 kHz, which is well within the operating range of the module. The current drawn from the module is also fairly low, as the channels are connected to high impedance inputs.

What could be the cause of this problem and how can it be solved?

Thanks!

Florian

Solved! Go to Solution.

04-12-2023 08:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are those waveforms captured from the NI-9401 ports directly? How can you be so sure that there is nothing wrong with your FPGA logic? Have you tried to log the output data using FPGA DMA FIFO?

Control Lead | Intelline Inc

04-12-2023 09:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Florian,

Echoing ZYOng here, have you inspected your LabVIEW FPGA and RT code? There are shipping examples for generating PWM signals from LabVIEW FPGA, you can find them in the LabVIEW Example Finder. Usually this code won't have any problems.

BR

John

Add motion to LabVIEW in 30min or less - TENET EMotion

Finding it hard to source NI hardware? Try NI Trading Post

04-13-2023 12:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The waveforms I have attached in the previous post are the amplified PWM signals. However, I have also measured the signals directly at the module’s ports. The signals at the ports and after the amplifier are basically the same, including the freezes, just at a different voltage level.

Today I have logged the computed PWM signals with DMA FIFO, right before they are passed to the I/O node for output. Even though some freezes were recorded with the measurement system, the logged signals from the FPGA looked perfectly fine.

I am using an additional NI-9401 module to communicate with a resolver to digital chip. I found out, that the outputs of this module are freezing too - at the exact same time. In the software, the computation and output of the PWM signals and resolver chip signals are done independently from each other.

04-13-2023 12:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have tried the "PWM Generation" example and only added an I/O node for signal output. No freezes occurred during the few minutes I ran this VI. Tomorrow I will do a longer test run, just to be sure.

04-17-2023 07:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have done some further testing with DMA FIFO and with some example VIs. The examples worked without any problems. I have also programmed some basic PWM VIs on my own, which also ran flawlessly.

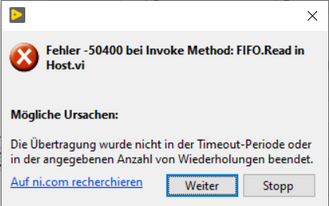

While doing some measurements with the DMA FIFO activated, I have noticed that the "Elements Remaining" counter from the Invoke Method "FIFO.Read" rises when the freeze occurs. After that, the number goes back to around zero. Sometimes the Host-VI showed the error 50400 – exactly at the same time as the freeze. When this error message shows up, the PWM outputs stay unresponsive until I click "Continue". Then the program continues to run as nothing had happened.

Something odd that I observed: whenever I scroll in the Host-VI window, the freezes occur very, very often – nearly every second. When I stop scrolling, the issue appears much less frequently.

04-19-2023 02:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I found the problem – it was the watchdog. As the program became more complex over time, the Host-VI loop that communicates with the FPGA is running at a lower rate than before. As a result, the watchdog signal could not be transmitted to the cRIO in time anymore, causing the FPGA-VI to stop. Since I also use the Invoke Method "Run" in this loop, the FPGA-VI was automatically restarted each time.

I was able to resolve all the mentioned problems only by adjusting the watchdog timeout.

04-26-2023 03:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nice! Glad everything worked out for you.

BR

John

Add motion to LabVIEW in 30min or less - TENET EMotion

Finding it hard to source NI hardware? Try NI Trading Post