- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Pulse width detection using NI USRP 2940R

03-29-2019 12:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am working on a project that receives RF pulses and verifies whether the pulses are valid or not by measuring the pulse width from half the maximum amplitude.

I want to implement all this logic using FPGA of NI USRP 2940R. Can anyone recommend me how I can implement this logic?

Regards,

M Mahboob Ur Rehman

05-03-2019 01:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi!

I would say after starting with the USRP Simple Streaming project in LabVIEW if you like to use the USRP FPGA.

Can you tell me about why it needs to be done on the FPGA? When you say RF Pulse do you mean a range of high frequences? Or are you talking a time domain pulse?

Best

NI Support

NI Technical Support Engineer

05-05-2019 01:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey,

1: Its need to be done in fpga because of time constraints. As after detection of Pulse, i need to output RF signal and this all needs to be performed within few micro seconds.

2: Yes its a high frequency pulse. And its shape is like a Gaussian pulse, as shown in picture.

I wanted to detect the pulse width of this gaussian pulse form half of the maximum amplitude.

Thanks

05-06-2019 12:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

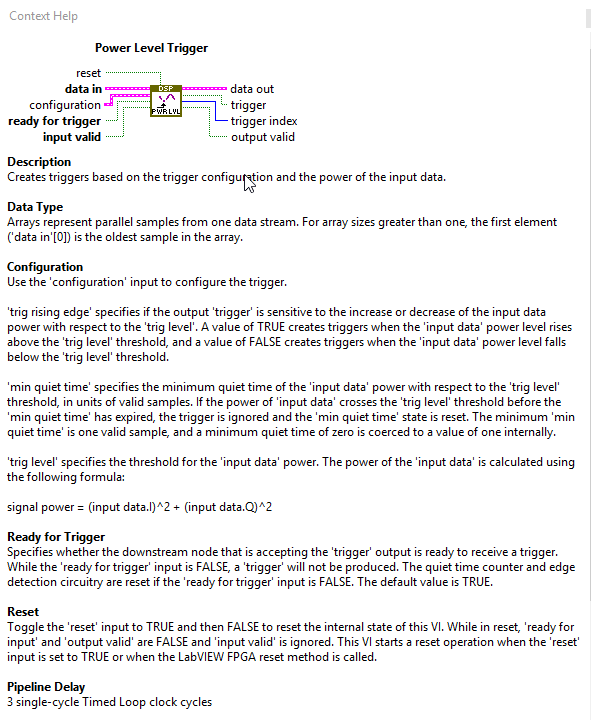

It looks like you may need to write logic for the FPGA to do that yourself. and it depends on what about the pulse we want to trigger on.

If it is a specific power level, there is a USRP Power Level Trigger VI on the DSP palette that would be utilized.

If you need that pulse specifically, it will get more complicated. You will likely need to implement some kind of peak amplitude detector and some logic to check the width of the pulse from that amplitude. Since it is an FPGA it will have to be point by point logic.

NI Technical Support Engineer

05-07-2019 03:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As power level of pulses changes continuously, therefore I think if I set trigger to specific power level. Then some pulses might got missed and hence this method will nor work for me.

Yes, I wanted to make some logic of peak amplitude detector and pulse width calculation within FPGA.

Regards,

M Mahboob Ur Rehman

05-08-2019 08:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Unfortunately, NI does not have any example code to offer for this application.

After a quick google I found this, and it looks promising

http://www.originalcode.com/downloads/Peak%20_Trigger_Long.doc

NI Technical Support Engineer

05-09-2019 12:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for sharing this. Some quality work has been explained. The idea that has been discussed in this work, having N samples delay and comparing it with real data,

I had also done some work on this principle of moving average and adaptive filter.

Regards

M Mahboob Ur Rehman