- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PXIe-5172 Compile Error -61499 "IO Resource has an invalid clock name specified for <RequiredClockDomain>"

Solved!04-13-2023 09:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

LabVIEW 2022 Q3

FlexRIO 22.8

NI-SCOPE 2022 Q3

LabVIEW 2022 Instrument Design Libraries for Reconfigurable Oscilloscopes

NI PXIe-1092 Chassis

NI PXIe-8881 Controller

NI PXIe-5172 8CH - 410T Reconfigurable Oscilloscope

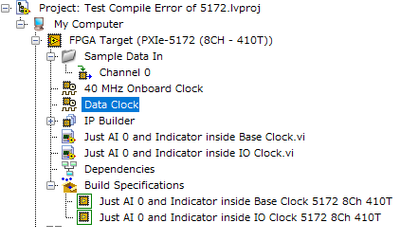

I can add the scope FPGA target just fine in the project.

I create a new FPGA IO for Channel0.

New VI with just the FPGA IO node and an indicator.

When I try to compile, I get the attached error:

<CodeGenErr>

<ErrorCode>-61499</ErrorCode>

<DynamicText>niFpgaReadWriteSetOutput_ValidateClockDomain.vi<-niFpgaDIOReadWriteSetOutput_SpecifyComponent.vi<-nirviEIOImplementation_CallTargetSpecifyComponent.vi:7310001<-niFpgaSpecifyComponent_nirviEIOImplementation.vi<-niFpgaSpecifyComponent_nirviEIOImplementation.vi.ProxyCaller

<APPEND>

<b>Additional Information:</b> IO Resource has an invalid clock name specified for <RequiredClockDomain></DynamicText>

</CodeGenErr>

What am I missing here? What am I doing wrong?

Solved! Go to Solution.

04-14-2023 02:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, what clock do you specify for SCTL inside which IO nodes are placed?

IO nodes for 5172's AI should be placed inside Data Clock domain. Maybe, your test code specifies different clock source for the SCTL. Data Clock can be added under FPGA target.

04-14-2023 10:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks! I was just using the default 40 MHz clock. I guess that doesn't work for this AI.

I had looked into the Data Clock, but was put off by the warning message:

"Warning: LabVIEW FPGA will not generate period constraint for this clock resource. Ensure that the clock period constraint is defined in the CLIP constraints file. The clock parameters specified here are required for LabVIEW FPGA to constraint clock domain crossings and to configure derived clocks from this clock resource. For information regarding creating or modifying the CLIP constraints file, please consult the LabVIEW Help and ni.com/support."

I wasn't using any CLIP so I thought this would be a problem.

04-14-2023 11:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Glad that setting data clock resolved the error. That makes sense. Do you have any reason starting from scratch rather than from Streaming or Multi Record Sample Project? Anyways, hope you have a great experiences with NI's open-FPGA oscilloscopes. It is definitely a great instrument customizable while easily used as just an oscilloscope with Instrument Studio.

04-14-2023 11:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I had trouble filtering the examples for the 5172 and wanted to start from absolute basics. I assumed the getting started instructions would discuss any need to explicitly add something like the Data Clock, but I guess not.

04-14-2023 11:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, I agree. NIs FPGA-related inventions had been so much wonderful but they had been horrible with communicating the wonderfuluness to outside world.

What are you planning to do with 5172? I have some experiences with 5172 and 5164. Let me know if you feel liike.

04-14-2023 12:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Reading a laser line scanner to capture an image of a moving topological surface.

04-14-2023 12:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What kind of implementation needed on FPGA of PXIe-5172? Does the trigger of laser timing come into as digital signal?

04-14-2023 12:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Syncing the AO that drives the orientation of the laser with PXI_Trig0

04-14-2023 12:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So, I assume triggers are generated first, then, some samples are acquired from AI for every trigger output. If it is in that case, please keep in mind that ADC pipelined delay should be considered inside SCTL. Accessing PFI lines or PXI trigger lines have less delay compared to AI node. Also, AI samples at 250MSps are handled two samples per cycle of SCTL at 125MHz. Therefore, the finiest resolution of timing between DO to AI acquisition is 8nsec.

If my assumptions are not correct, just ignore this post. Enjoy your development!