- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

External Trigger based data acquisition

12-01-2014 09:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Our input signal is pulsed generated by a signal generator. Along with RF pulse, a LVTTL Trigger is also generated by a signal generator and both of them are synchronized in time.

Pulsewidth=4usec

Pulse Period=300 uses

I have connected both of them with USRP-RIO and run the streamibg example. Trigger settings in exampme was changed to external-trigger.

Then i observed the output on graph. As expected the RF pulse power was in the start of the graph and was static showing that data is being acquired based on trigger rising edge. But there are still two problems

1: The RF pulse is not exactely at 1st sample and the initial delay varies randomly at differnt runs of program. But during a single run, the delay remains constant.

2: Sometimes the RF pulse starts running on graph showing that data is not not acquired properly based on trigger edge.

We also have a VST 5644 with us. We tested the same setup with VST streaming example and the behaviour of acquired data based on external trigger is totally correct.

so it seems that streaming example code of USRP -RIO might have some issue with causes inaccurate acquisition based on external trigger.

Thanks,

Adeel

12-02-2014 05:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi AdeelAnwar,

What version of NI-USRP are you using, and how are you connecting your signal to the USRP-RIO?

What VI are you opening within the USRP Streaming project - and where are you modifying the trigger to be an external trigger?

Thanks!

12-02-2014 08:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am using NI USRP 14.0 with labview 2013.

Rf out of signal generator is connected to USRP RX port. Trigger out of signal generator is connected with USRP-RIO DIO-0.

Main host VI of sample project. "Software Trigger" drop down menu was changed to "External Trigger" and Rx mode to "Burst (Finite samples)"

-Adeel

12-03-2014 03:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Adeel,

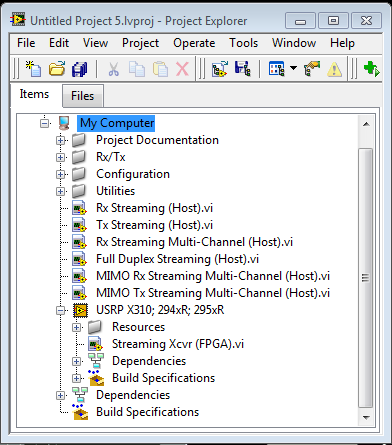

I'm having trouble finding the exact VI you're using and settings you're changing. In order to create a USRP RIO sample streaming project, I load LabVIEW, select "Create Project", select "NI-USRP" in the left pane, and open the "Simple NI-USRP Streaming" example.

I then have this project window:

Is your project similar? And if so, which VI are you changing your settings in?

12-03-2014 10:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Rick,

I am using "Rx Streaming (Host)" vi. with the settings shown in figure below. Sampling-rate is 3.125 MSPS and num-samples=1040.

I have also attached the figure of "Start-Trigger" which is a subVI of "Streaming XCVR FPGA", where AUX I/O-0 is acts as the source of trigger when we select "Digital-Edge" in the Host VI.

Thanks,

Adeel

12-05-2014 09:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Adeel,

I was able to find the settings - thanks for those images!. Now let's talk about the two issues you were having:

1: The RF pulse is not exactely at 1st sample and the initial delay varies randomly at differnt runs of program. But during a single run, the delay remains constant.

When you say "not exactly" at the first sample, do you mean that you receive multiple digital edges before acquisition begins, or there's a delay from the rising edge of the trigger? For the delay that you're seeing, how much of a delay, in general, do you see?

2: Sometimes the RF pulse starts running on graph showing that data is not not acquired properly based on trigger edge.

Could you elaborate on this? Perhaps some images of what you're trying to describe could be helpful as well.

Thanks.

12-09-2014 07:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Signal generator is generating RF-pulse and a TTL Trigger. Both of them start and end at the same time. I hv checked this using an Oscilloscope.

I am giving both of these signal to USRP-RIO. Ideally the RF pulse should start on 1st sample of the acquired burst bcz the input digital trigger is synchronized with it. This doesnot happen instead RF-pulse starts after initial "k" samples where k depends on the sampling-rate. Currently i am using 3.125MSPS and acquired RF-pluse is being observed using waveform-graph.

I found out that this maybe due to the fractional interpolator/decimator chain which comes after ADC. If this delay remains fixed then this is not an issue as it can be catered of by ignoring initial samples. But there are two problems

1: "K" doesnot remain constant in different runs of program i.e. if i run the streaming example the pulse start maybe after 8 samples. Now if i stop the streaming example and run it again then the pulse start maybe after 12 samples.

Moreover this doesnot happen if i set the sampling-rate to 1MSPS but when i set the samplind rate to 3.135MSPS this happens. (Note external signal from signal generator pulsewidth=10 usec pulse-period=3khz)

As mentioned above that at different runs of Streaming example i observe different "k". But in a single run this delay remains constant.

2: The other problem is that sometimes when this example is running 'k' starts to vary randomly and this causes the displayed RF-Pulse to move back and forth on the waveform-graph.

Thanks,

12-09-2014 07:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

12-09-2014 07:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

But 3.135:120 is giving you an offset that could vary by some number of samples, somewhere between 8 and 12 in your testing. Does that sound like the behavior you see?

Does another integer sample rate like 3 or 5 mS/s go back to a fixed k?

12-09-2014 07:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator