View Ideas...

Labels

-

Analysis & Computation

301 -

Development & API

2 -

Development Tools

1 -

Execution & Performance

1,004 -

Feed management

1 -

HW Connectivity

113 -

Installation & Upgrade

264 -

Networking Communications

181 -

Package creation

1 -

Package distribution

1 -

Third party integration & APIs

280 -

UI & Usability

5,387 -

VeriStand

1

Idea Statuses

- New 2,988

- Under Consideration 11

- In Development 1

- In Beta 0

- Declined 2,628

- Duplicate 708

- Completed 329

- Already Implemented 114

- Archived 0

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

LV2010 Merge Errors Improvement

Submitted by

JB

on

08-18-2010

10:28 AM

14 Comments (14 New)

JB

on

08-18-2010

10:28 AM

14 Comments (14 New)

Status:

New

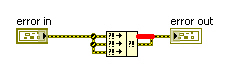

Unlike the other growable functions (eg Build Array, Concatenate Strings), the output of the really appreciated new Merge Errors function shouldn't be centered to avoid a bend in the error wire.

Labels:

14 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

Re-opening this idea due to the discontinuation of LabVIEW NXG.